4 smc functional operation, 1 operating states, Smc functional operation -15 – SMC Networks ARM PL241 User Manual

Page 35: Figure 2-10, Smc aclk domain fsm -15

Functional Overview

ARM DDI 0389B

Copyright © 2006 ARM Limited. All rights reserved.

2-15

2.4

SMC functional operation

This section describes:

•

•

Clocking and resets on page 2-16

•

Miscellaneous signals on page 2-18

•

APB slave interface operation on page 2-19

•

•

Memory manager operation on page 2-22

•

Interrupts operation on page 2-27

•

Memory interface operation on page 2-27.

2.4.1

Operating states

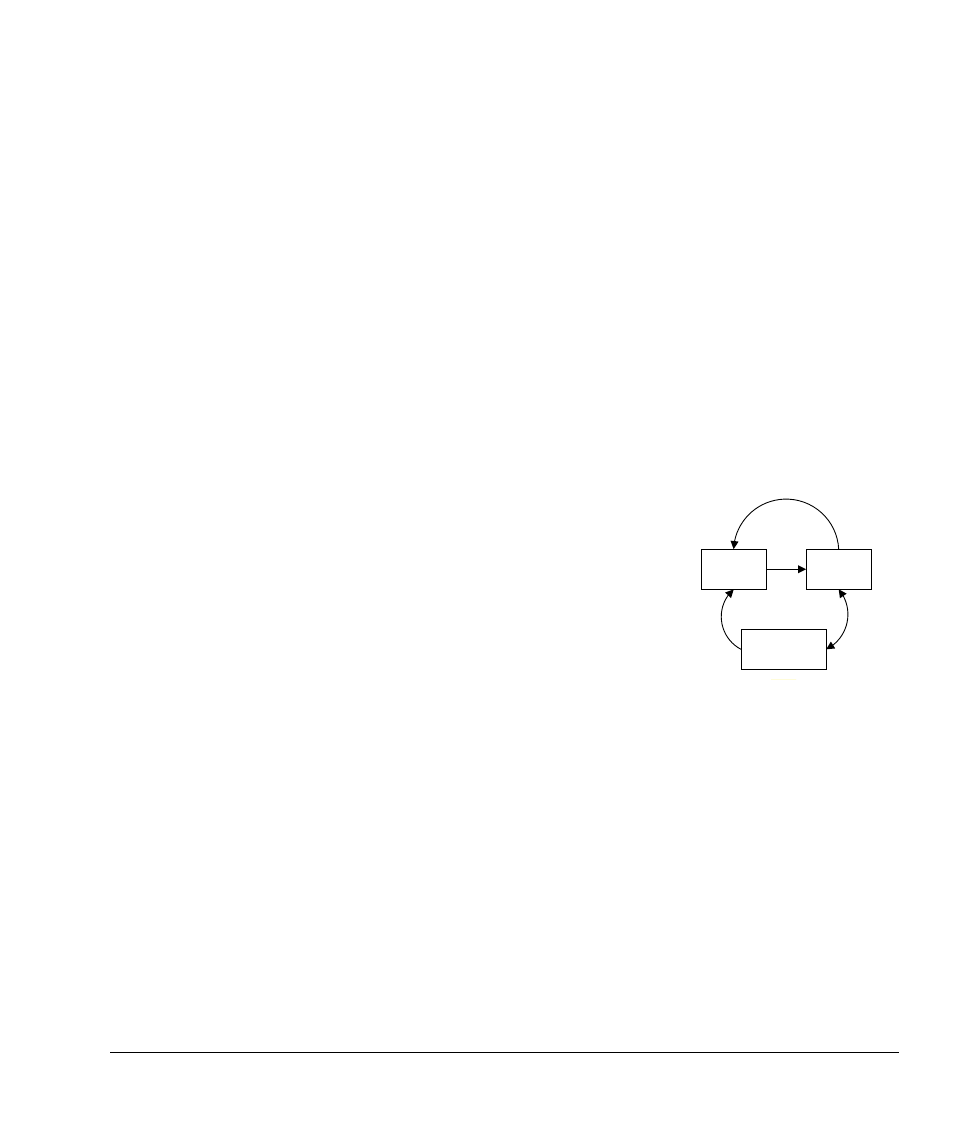

The operation of the SMC is based on three operating states. In this section, each state

is described. Figure 2-10 shows the state machine.

Figure 2-10 SMC aclk domain FSM

The SMC states are as follows:

Reset

Power is applied to the device, and hresetn is held LOW.

Ready

Normal operation of the device. You can access the SMC register bank

through the AHB configuration port and external memory devices

accessed through the SMC interface.

Low-power The device does not accept new AHB transfers, and only certain registers

are accessible through the APB interface. You can stop the SMC clocks

to reduce power consumption.

5HVHW

5HDG\

/RZSRZHU