3 clock domains, 4 low-power interface, Figure 2-2 – SMC Networks ARM PL241 User Manual

Page 23: Ahb mc (pl241) clock domains -3

Functional Overview

ARM DDI 0389B

Copyright © 2006 ARM Limited. All rights reserved.

2-3

2.1.3

Clock domains

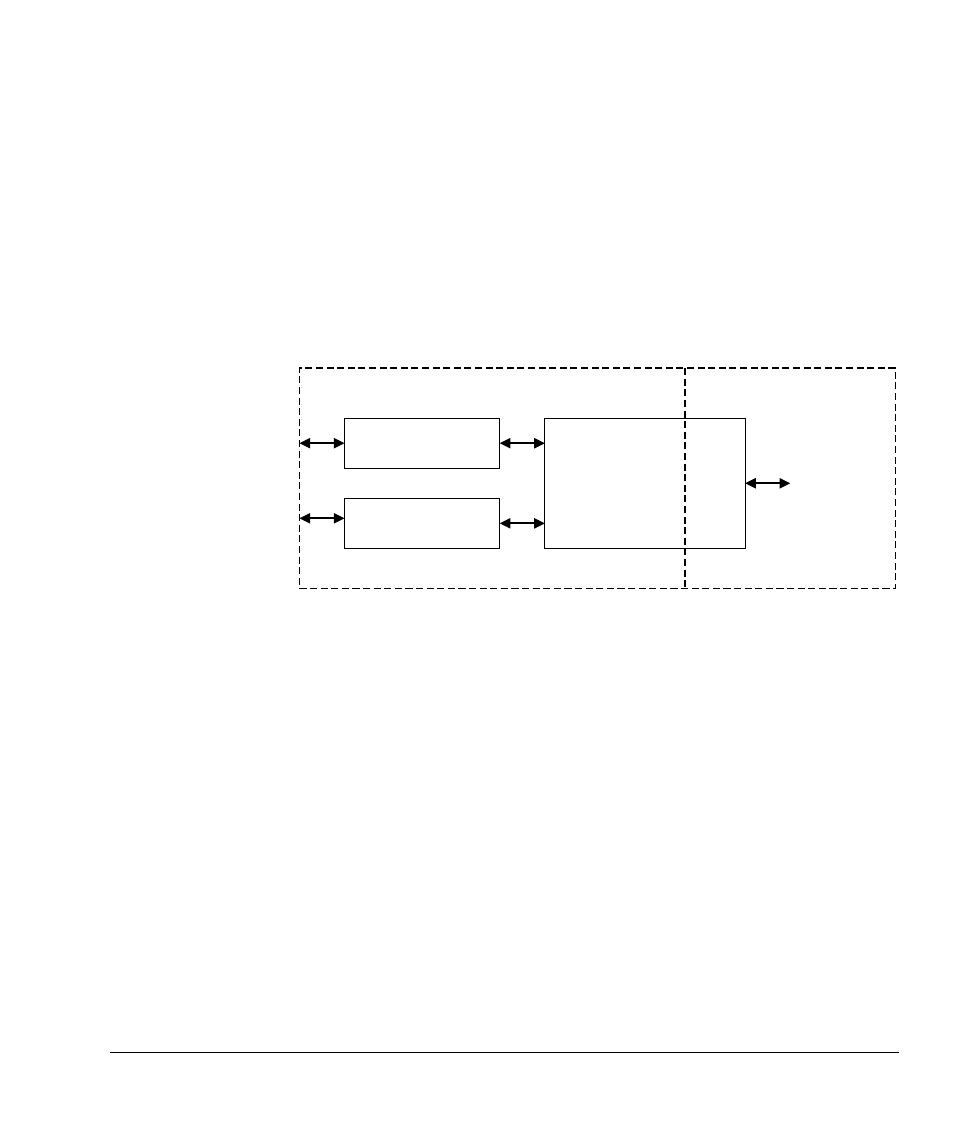

The memory controller has two clock domains:

AHB clock domain

This is clocked by hclk, smc_aclk and reset by hresetn.

Static memory clock domain

This is clocked by smc_mclk0, smc_mclk0n and reset by

smc_mreset0n.

Figure 2-2 shows the two clock domains.

Figure 2-2 AHB MC (PL241) clock domains

The memory controller supports many different options for clocking the different

domains.

See Clock domain operation on page 2-11 for more information.

2.1.4

Low-power interface

The memory controller has two low-power interfaces, one for each clock domain. These

operate with a simple three signal protocol. It is expected that a system clock controller

drives these interfaces and associated clocks. Each domain has individual control to

enable independent handshaking with the system clock controller.

See Low-power interface operation on page 2-12 for more information.

$+%LQWHUIDFH

60&

$+%0&3/

$+%WR$3%

EULGJH

$+%

$3%6

$+%

FRQILJXUDWLRQ

SRUW

6

0

0

65$0

PHPRU\

VPFBPFON

VPFBDFON

KFON

$+%FORFNGRPDLQ

6WDWLFPHPRU\FORFNGRPDLQ