6 pad interface, 7 interrupts, Figure 2-4 – SMC Networks ARM PL241 User Manual

Page 26: Smc sram pad interface external connections -6

Functional Overview

2-6

Copyright © 2006 ARM Limited. All rights reserved.

ARM DDI 0389B

2.2.6

Pad interface

The pad interface module provides a registered I/O interface for data and control

signals. It also contains interrupt generation logic.

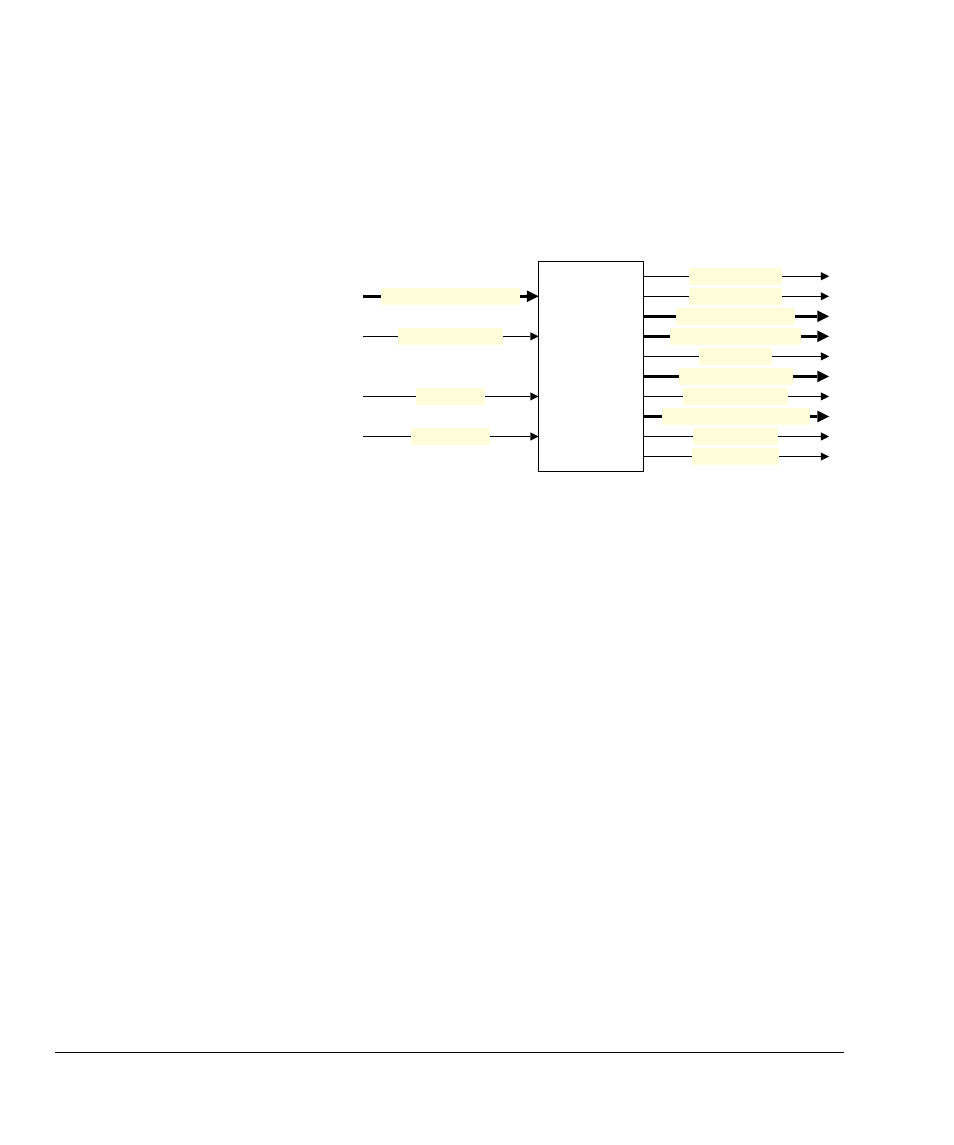

Figure 2-4 shows the SRAM pad interface external signals. Clock and reset signals are

omitted.

Figure 2-4 SMC SRAM pad interface external connections

2.2.7

Interrupts

The SRAM memory interface support interrupts. The interrupt is triggered on the rising

edge of the smc_int_0 input for the SRAM memory interface.

See Interrupts operation on page 2-27 for more information.

65$0

SDGLQWHUIDFH

VPFBGDWDBLQB>@

VPFBZDLWB

VPFBLQWB

VPFBFONBRXWB>@

VPFBFVBQB>@

VPFBZHBQB

VPFBRHBQB

VPFBEOVBQB>@

VPFBDGYBQB

VPFBEDDBQB

VPFBGDWDBRXWB>@

VPFBGDWDBHQB

VPFBIEFONBLQB

VPFBFUHB