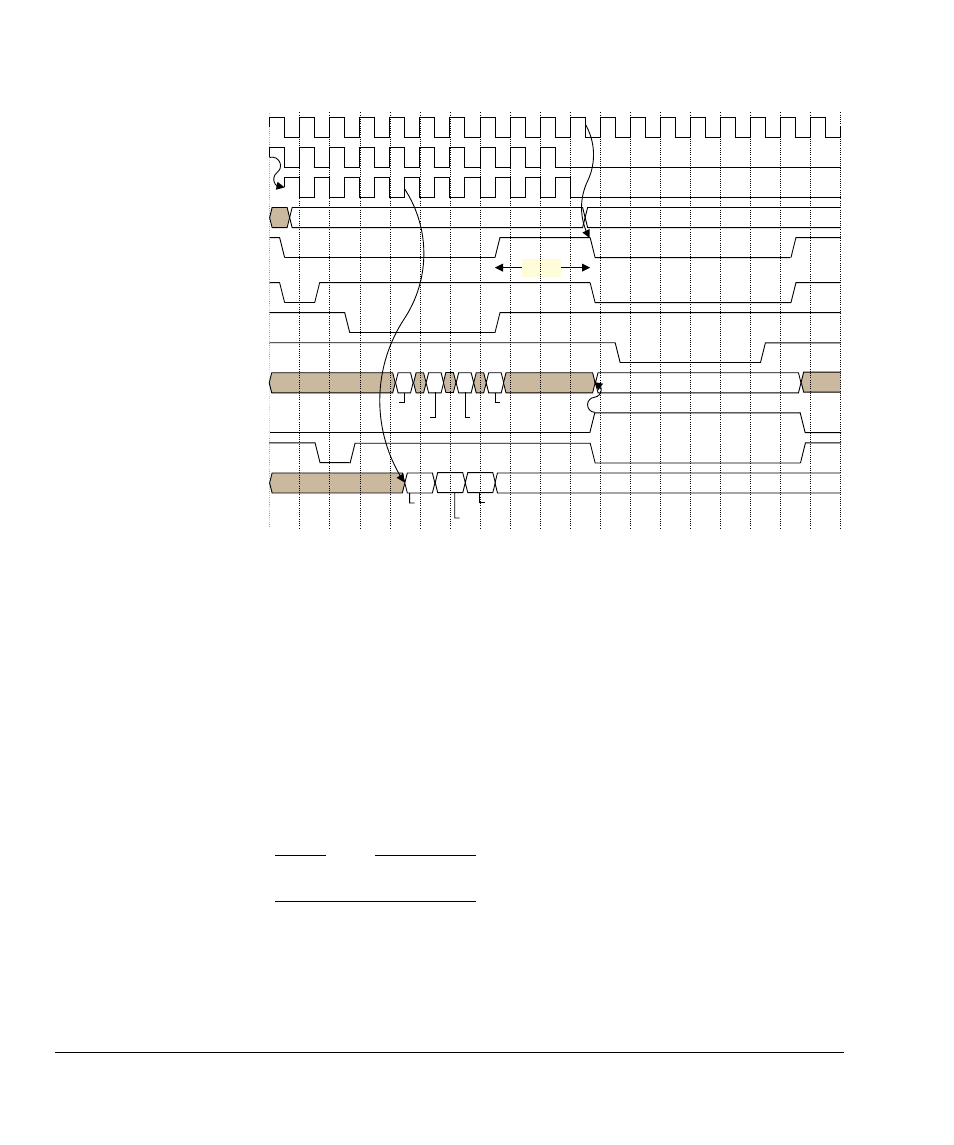

Figure 2-23, Synchronous read and asynchronous write -38 – SMC Networks ARM PL241 User Manual

Page 58

Functional Overview

2-38

Copyright © 2006 ARM Limited. All rights reserved.

ARM DDI 0389B

Figure 2-23 Synchronous read and asynchronous write

Programming t

RC

and t

WC

when the controller operates in synchronous mode

For t

RC

:

•

when using memory devices that are not wait-enabled, you must program t

RC

to

be the number of clock cycles required before valid data is available following the

assertion of cs_n

•

when using memory devices that are wait-enabled, you must program t

RC

to be

the number of clock cycles required before wait is active and stable, following the

assertion of cs_n. That is:

t_RC = 3 + t_CEOE

Note

t_CEOE is only required if wait is asserted when oe_n goes LOW.

VPFBPFON

VPFBFONBRXWB>@

VPFBIEFONBLQB

VPFBDGGB>@

$''5$

$''5%

VPFBFVBQB>@

VPFBDGYBQB

W

75

VPFBRHBQB

VPFBZHBQB

GDWD

'%

'$

'$

'$

'$

VPFBGDWDBHQB

GDWD

UHDGBGDWD

'$

'$

'$

'$