Table 2-8, Table 2-9, Table 2-10 – SMC Networks ARM PL241 User Manual

Page 51: Table 2-11, Figure 2-17, Asynchronous write in multiplexed-mode -31

Functional Overview

ARM DDI 0389B

Copyright © 2006 ARM Limited. All rights reserved.

2-31

Asynchronous write in multiplexed-mode

Table 2-8 and Table 2-9 list the smc_opmode0_<0-3> and SRAM Register settings.

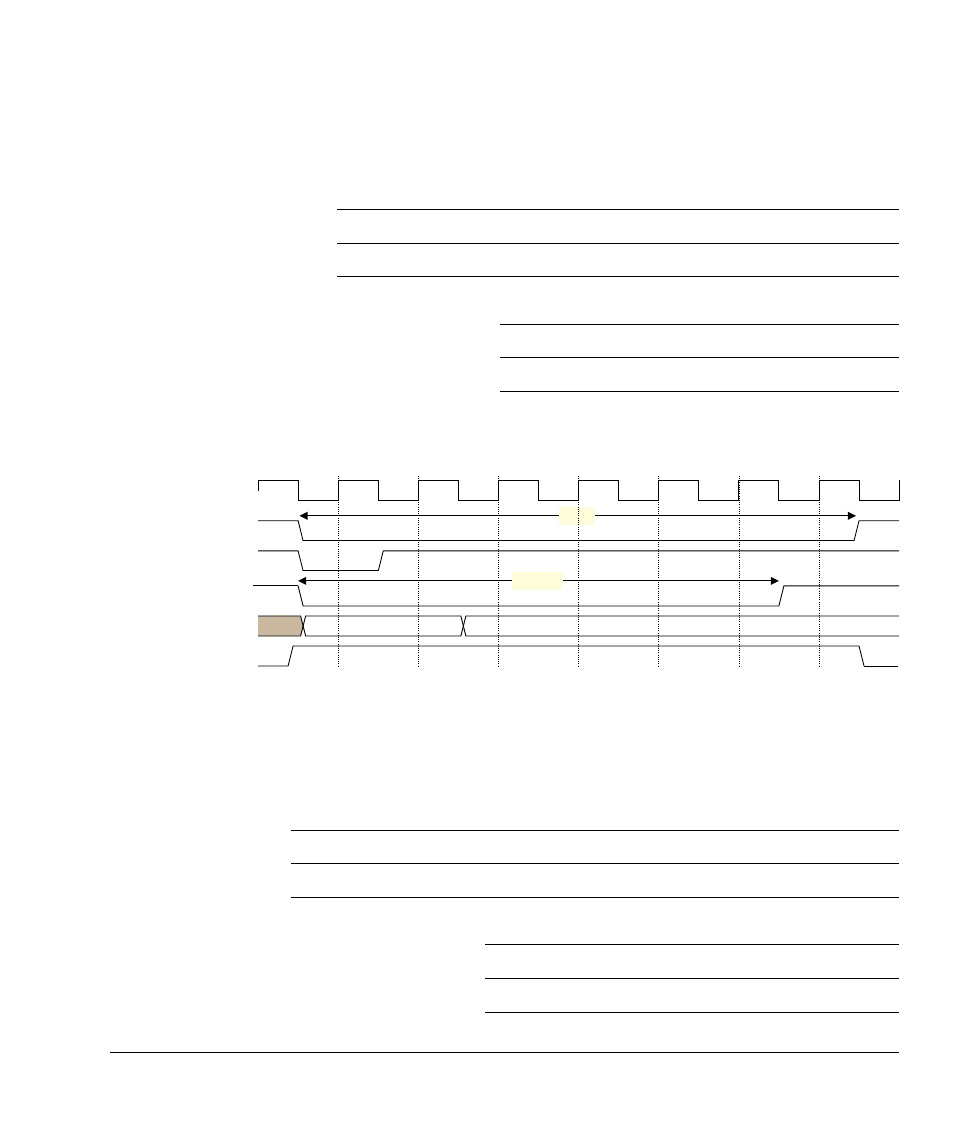

Figure 2-17 shows an asynchronous write in multiplexed-mode. t

WC

is seven cycles. t

WP

is four cycles, and is extended by two cycles for the address phase of the transaction.

Figure 2-17 Asynchronous write in multiplexed-mode

Asynchronous page mode read

Table 2-10 and Table 2-11 list the smc_opmode0_<0-3> and SRAM Register settings.

Table 2-8 Asynchronous write in multiplexed-mode opmode chip register settings

Field

mw

rd_sync

rd_bl

wr_sync

wr_bl

baa

adv

bls

ba

Value

-

-

-

b0

b000

b0

b0

-

-

Table 2-9 Asynchronous write in multiplexed-mode SRAM cycles register settings

Field

t_rc

t_wc

t_ceoe

t_wp

t_pc

t_tr

Value

-

b0111

-

b100

-

-

VPFBPFON

VPFBFVBQB>@

VPFBDGYBQB

VPFBGDWDBHQB

VPFBZHBQB

VPFBGDWDBRXWB>@

W

:&

W

:3

'

$

Table 2-10 Page read opmode chip register settings

Field

mw

rd_sync

rd_bl

wr_sync

wr_bl

baa

adv

bls

ba

Value

-

b0

-

-

-

-

-

b1

Table 2-11 Page read SRAM cycles register settings

Field

t_rc

t_wc

t_ceoe

t_wp

t_pc

t_tr

Value

b0011

-

b010

-

b001

-