5 decoupling guidelines: intel, 440gx agpset platform – Intel 440GX User Manual

Page 55

Intel

®

440GX AGPset Design Guide

2-31

Motherboard Layout and Routing Guidelines

Because of the specifics of an ATX layout, it is recommended that the PIIX4E component is at the

“END” of the PCI bus, as shown in

Figure 2-28

. This insures proper “termination” of the PCI Bus

signals.

2.9.5

Decoupling Guidelines: Intel

®

440GX AGPset Platform

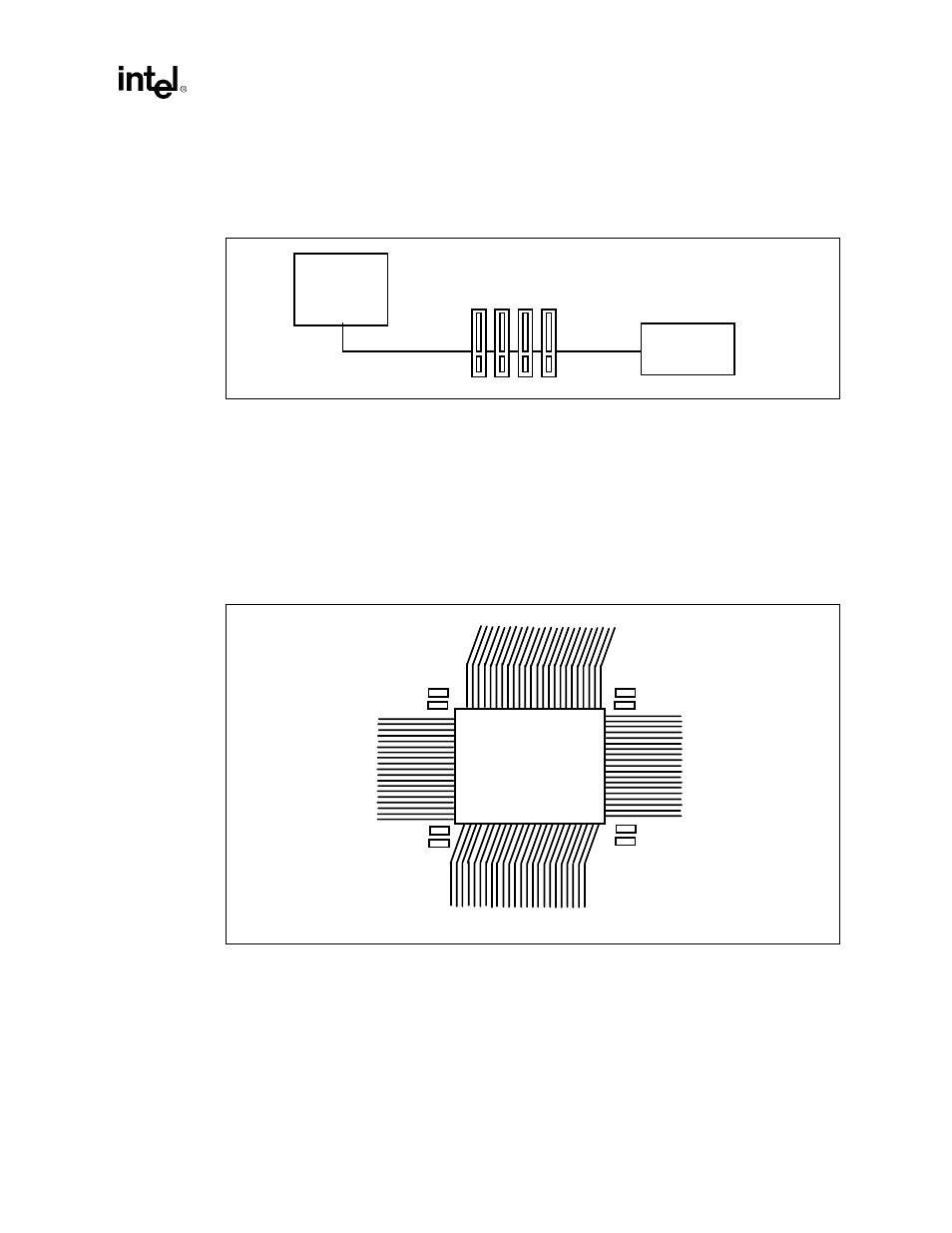

Decoupling caps should be placed at the corners of the 443GX(BGA Package). A minimum of four

0.1uF and four 0.01 uF are recommended. The system bus, AGP, PCI, and DRAM interface can

“break-out” from the BGA package on all four sides. Additional caps will also help reduce EMI

and cross-talk.

Note:

There are other discrete components for V

TT

, GTL Ref Voltages that must be also considered when

routing around the 82443GX.

Figure 2-28. PCI Bus Layout Example

82443GX

PIIX4E

Figure 2-29. 82443GX Decoupling

82443GX

Host Bridge

Controller

492 BGA

0.1uF

0.01uF

0.1uF

0.01uF

0.1uF

0.01uF

0.1uF

0.01uF

v006

- 41210 (64 pages)

- 8xC251TQ (20 pages)

- ENTERPRISE PRINTING SYSTEM (EPS) 4127 (84 pages)

- U3-1L (20 pages)

- 80960HA (104 pages)

- X58 (54 pages)

- ESM-2850 2047285001R (91 pages)

- ATOM US15W (54 pages)

- D915GVWB (4 pages)

- XP-P5CM-GL (28 pages)

- AX965Q (81 pages)

- CORETM 2 DUO MOBILE 320028-001 (42 pages)

- CV700A (63 pages)

- 80C188EA (50 pages)

- X25-M (28 pages)

- XP-P5IM800GV (26 pages)

- IB868 (60 pages)

- D865GVHZ (88 pages)

- IB865 (64 pages)

- Altera P0424-ND (1 page)

- 8086-2 (30 pages)

- IXDP465 (22 pages)

- IWILL P4D (104 pages)

- GA-8I955X PRO (88 pages)

- FSB400 (PC2100) (96 pages)

- D845GLAD (4 pages)

- NAR-3041 (1 page)

- 87C196CA (136 pages)

- G52-M6734XD (74 pages)

- A96134-002 (10 pages)

- Express Routers 9000 (8 pages)

- 82540EP (45 pages)

- D865GLC (94 pages)

- IB850 (69 pages)

- MB898RF (62 pages)

- Arima LH500 (78 pages)

- V09 (33 pages)

- I/O Processor (22 pages)

- M600 (110 pages)

- SE7520JR2 (63 pages)

- SERVER BOARD S5520HCT (30 pages)

- Extensible Firmware Interface (1084 pages)

- GA-8IPXDR-E (70 pages)

- D845EBG2 (4 pages)

- AW8D (80 pages)