E.4.1 command linking and queuing – Intel Extensible Firmware Interface User Manual

Page 905

32/64-Bit UNDI Specification

Version 1.10

12/01/02

E-39

NOTE

Additional requirements for S/W UNDI implementations: Processor register contents must be

unchanged by S/W UNDI command execution (the application/driver does not have to save

processor registers when calling S/W UNDI). Processor arithmetic flags are undefined

(application/driver must save processor arithmetic flags if needed). Application/driver must

remove CDB address from stack after control returns from S/W UNDI.

NOTE

Additional requirements for 32-bit network devices: All addresses given to the S/W UNDI must be

32-bit addresses. Any address that exceeds 32 bits (4 GB) will result in a return of one of the

following status codes: PXE_STATCODE_INVALID_PARAMETER,

PXE_STATCODE_INVALID_CDB or PXE_STATCODE_INVALID_CPB.

When executing linked commands, command execution will stop at the end of the CDB list (when

the

PXE_CONTROL_LINK

bit is not set) or when a command returns an error status code.

E.4.1

Command Linking and Queuing

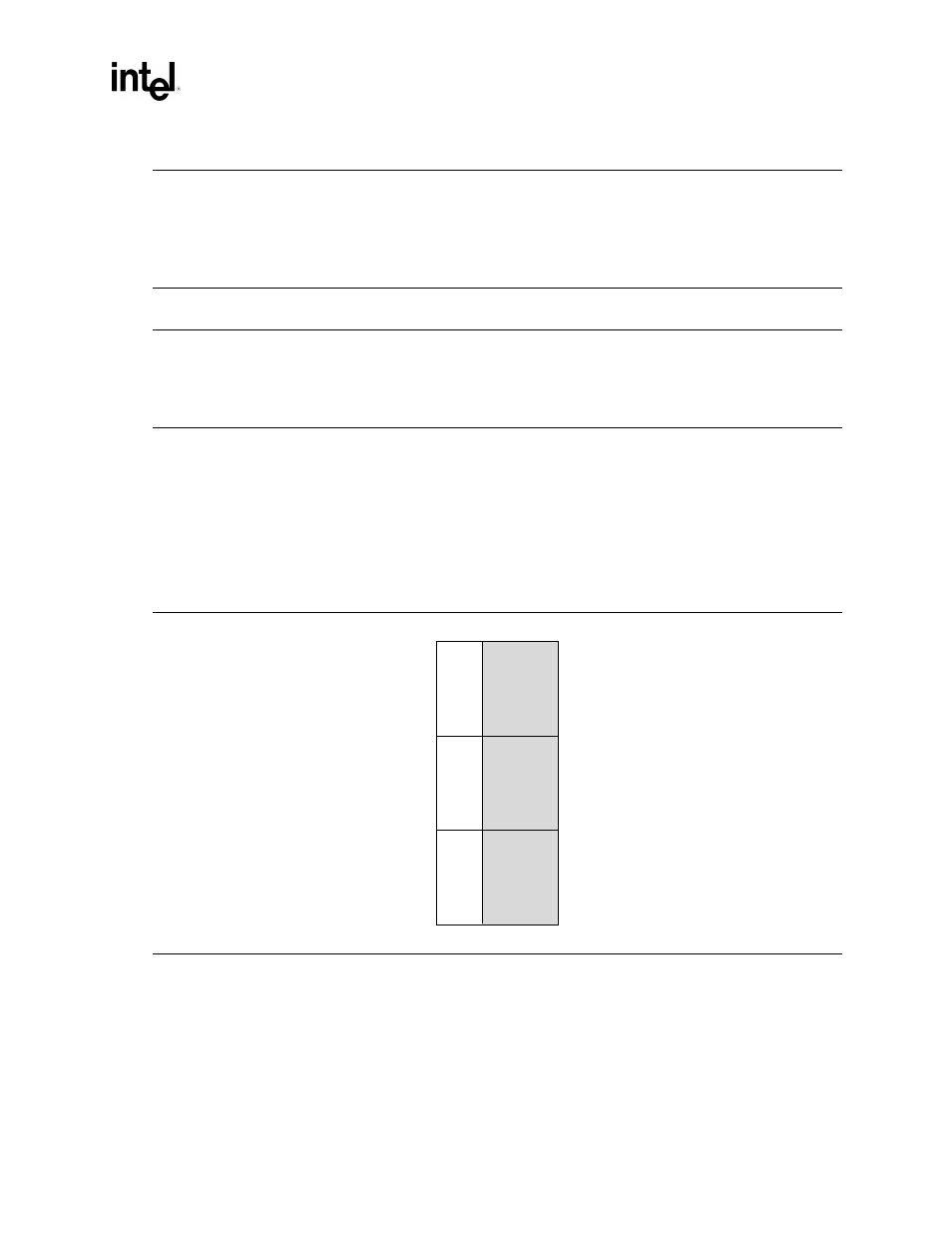

When linking commands, the CDBs must be stored consecutively in system memory without any

gaps in between. Do not set the Link bit in the last CDB in the list. As shown in Figure E-7, the

Link bit must be set in all other CDBs in the list.

OM13188

Linked CDBs

0x00

0x1F

0x20

0x3F

Set Link bit.

0x40

0x5F

Set Link bit.

Do not set

Link bit.

CDB

CDB

CDB

Figure E-7. Linked CDBs