Behaviors and restrictions – Intel Extensible Firmware Interface User Manual

Page 804

Extensible Firmware Interface Specification

19-30

12/01/02

Version 1.10

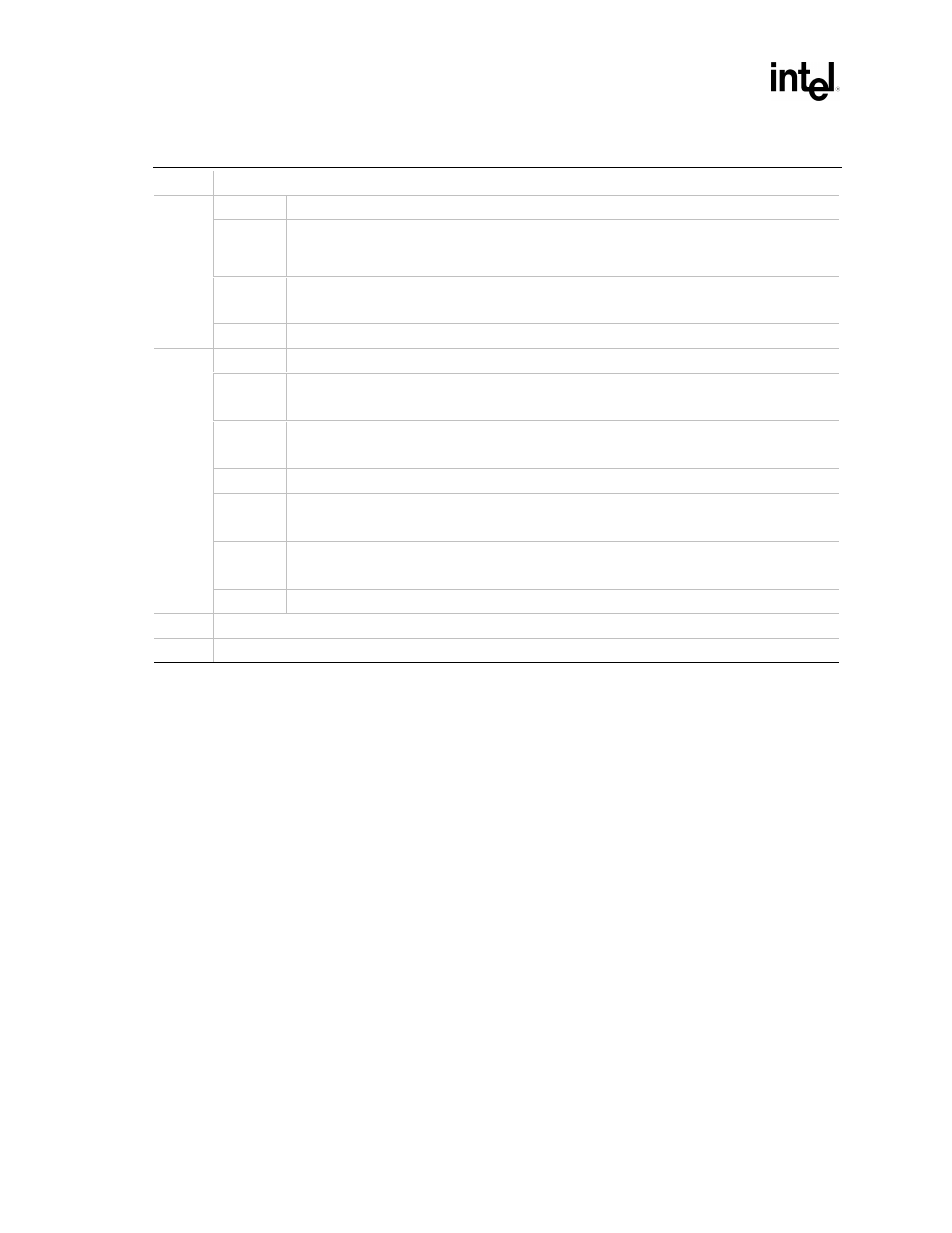

Table 19-21 JMP Instruction Encoding

BYTE DESCRIPTION

Bit Description

7

0 = Immediate/index data absent

1 = Immediate/index data present

6

0 = JMP32

1 = JMP64

0

0..5

Opcode = 0x01

Bit Description

7

0 = Unconditional jump

1 = Conditional jump

6

0 = Jump if

Flags.C

is clear (cc)

1 = Jump if

Flags.C

is set (cs)

5

Reserved = 0

4

0 = Absolute address

1 = Relative address

3

0 = Operand 1 direct

1 = Operand 1 indirect

1

0..2 Operand

1

2..5

Optional 32-bit immediate data/index for JMP32

2..9

64-bit immediate data for JMP64

BEHAVIORS AND RESTRICTIONS:

• Operand 1 fields are ignored for the JMP64 forms

• If the instruction is JMP32, and Operand 1 register = R0, then the register contents are assumed

to be 0.

• If the instruction is JMP32, and Operand 1 is indirect, then the immediate data is interpreted as

an index, and the jump offset or address is fetched as a 32-bit signed value from address [R

1

+

Index32]

• If the instruction is JMP32, and Operand 1 is direct, then the immediate data is considered a

signed immediate value such that Operand 1 = R

1

+ Immed32

• If the jump is unconditional, then Byte1:Bit6 (condition) is ignored

• If the instruction is JMP64, and Byte0:Bit7 is clear (no immediate data), then an instruction

encoding exception is generated.

• If the instruction is JMP32, and Operand 2 is indirect, then the Operand 2 value is read as a

natural value from memory address [R

1

+ Index32]

• An alignment check exception is generated if the jump is taken and the target address is odd.