FUJITSU MCE3130AP User Manual

Page 102

4 - 34

C156-E142-02EN

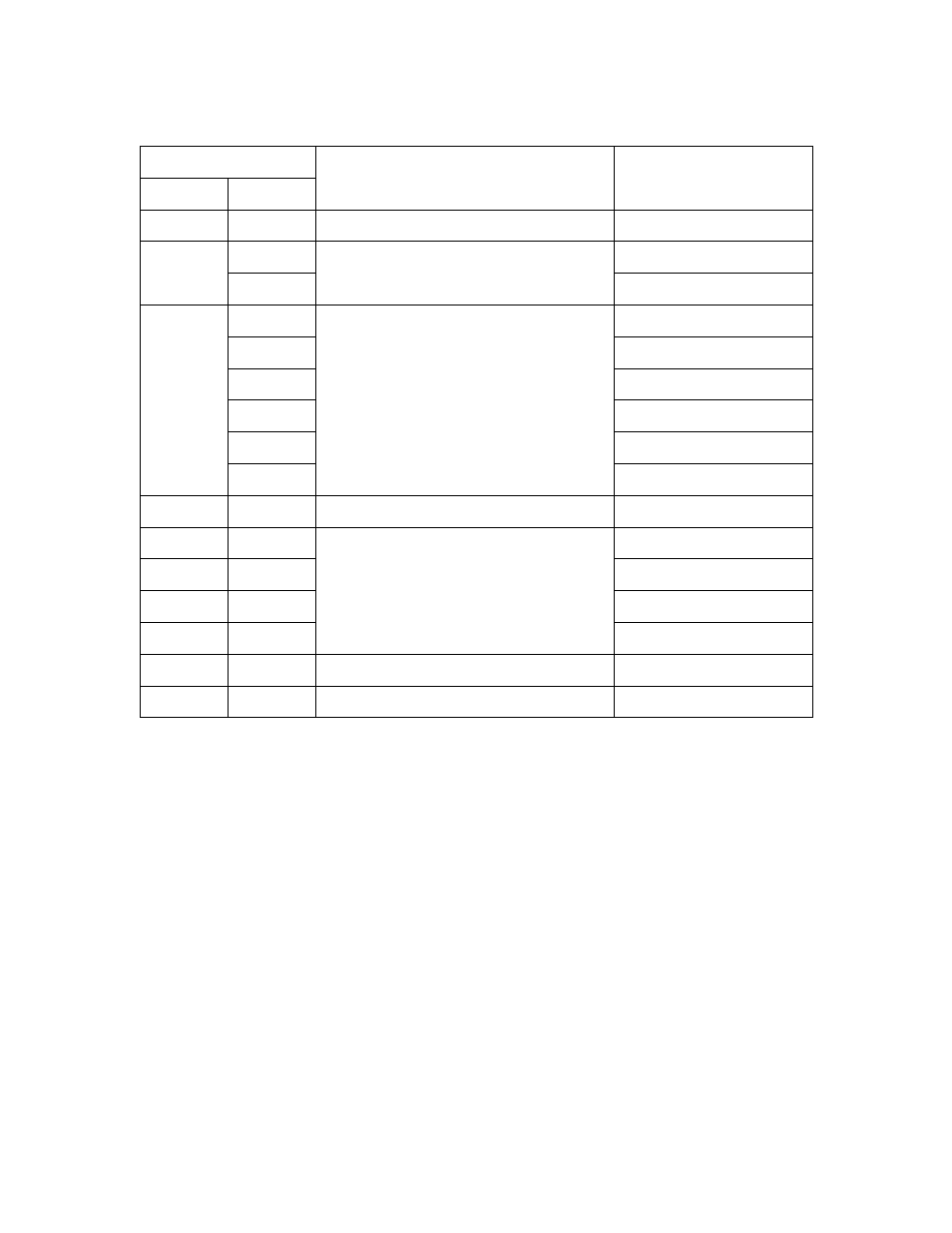

Table 4.34 Transfer setting values in the SC register

Setting value

Function

ODD response

Bits 7 to 3

bits 2 to 0

00000

000

PIO default transfer mode

Normally end

00000

001

PIO default transfer mode

Normally end

010 to 111

(without IORDY signal)

Report Aborted Command

00001

000

PIO flow control transfer mode

Normally end

001

(with IORDY signal)

Normally end

010

Normally end

011

Normally end

100

Normally end

101 to 111

Report Aborted Command

00010

000 to 111

Reserved

Report Aborted Command

00100

000

Multiword DMA transfer mode

Normally end

00100

001

Normally end

00100

010

Normally end

00100

011 to 111

Report Aborted Command

01000

000 to 111

Reserved

Report Aborted Command

10000

000 to 111

Reserved

Report Aborted Command

When the FR register is X'95', the ODD responds with the following value at the end of the

command.

! The CL register is set with X'00'.

! The CH register is set as shown below.