Dac960prl block diagram (sisl) – Avago Technologies AcceleRAID 150 User Manual

Page 58

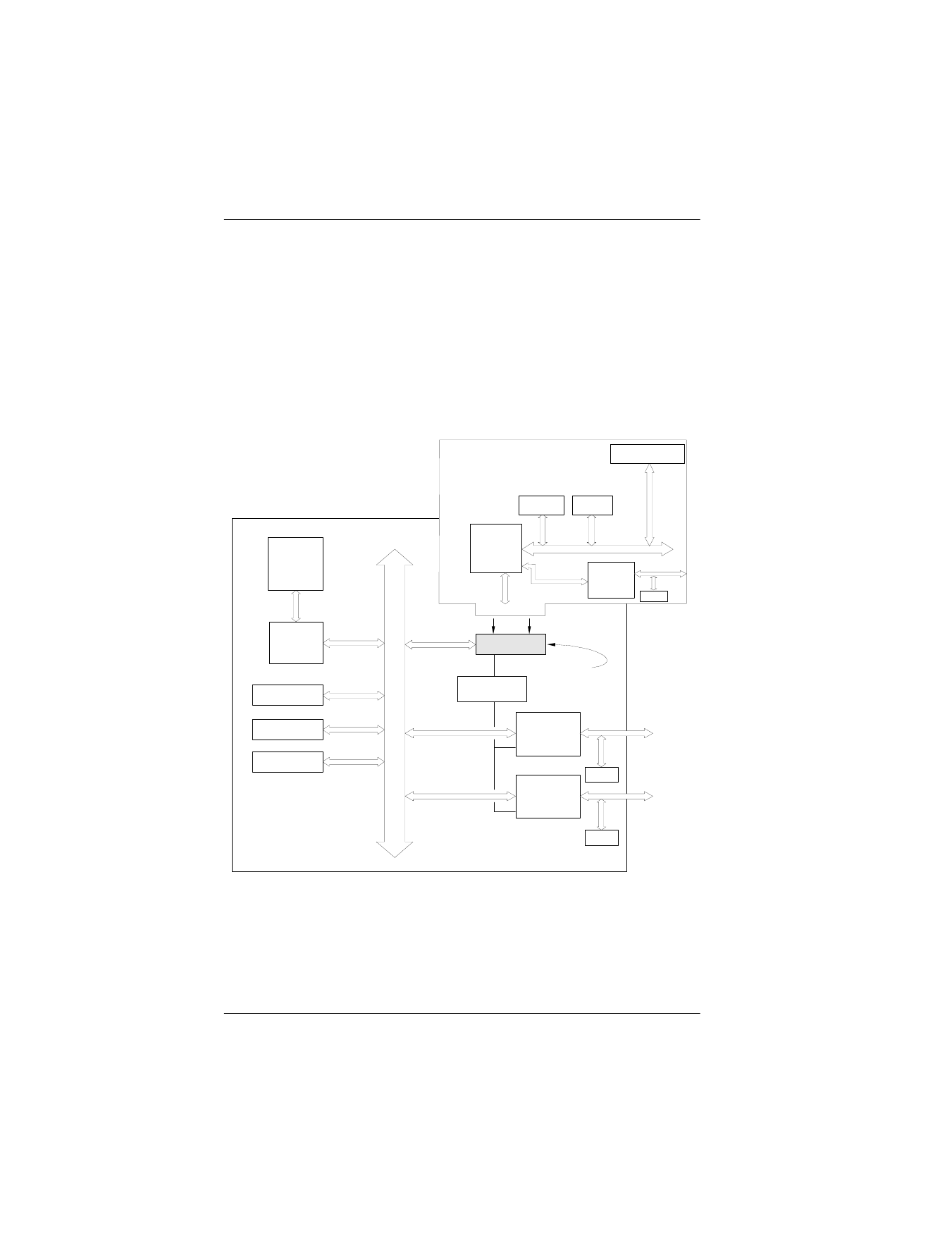

DAC960PRL Block Diagram (SISL)

B-4

AcceleRAID 150 Installation Guide

DAC960PRL Block Diagram (SISL)

Figure B-2 (example of a system board block diagram) shows the functional

relationship between the Mylex AcceleRAID 150 Controller and the SCSI-

capable system board. The SCSI chip interrupt line(s) are routed to a PCI bus

slot (shaded to indicate SISL availability) specifically preconfigured to

accept the controller.

The non-shaded PCI bus slots indicate an example of available SCSI

connections that are not intended for SISL activity.

Figure B-2. AcceleRAID and SCSI-Capable System Board (SISL)

CPU

PCI Interface

Control

Logic

PCI Bus Slot

PCI Bus Slot

PCI Bus Slot

PCI Bus Slot

SCSI Protocol

Chip

SCSI Protocol

Chip

Term.

Term.

SCSI Bus

SCSI Bus

PCI Slot

Pre-configured

for AcceleRAID

System Board

Interrupt Logic

RAID FW

NVRAM

Cache Memory

I960RP

AcceleRAID 150

DAC960PRL

Controller

Term.

SCSI

Protocol

Chip

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)