Dac chab register b 0x4b – Sundance SMT942 User Manual

Page 44

User Manual SMT942

Page 44 of 55

Last Edited: 23/08/2011 17:25:00

DAC Chab Register A 0x4A

Setting

Bit 7:0

Description Ser_dac_data[7:0]

0

0

Setting

Bit 9:8

Description qmoffset_reg_sel selects sync for loading the QM offset register

0

‘00’

TXENABLE from FIFO output

0

‘01’

SYNC from FIFO output

1

‘10’

Sync_sif_sig

1

‘11’

Always 0

Setting

Bit 11:10

Description qmcorr_reg_sel selects sync for loading the QM correction register

0

‘00’

TXENABLE from FIFO output

0

‘01’

SYNC from FIFO output

1

‘10’

Sync_sif_sig

1

‘11’

Always 0

Setting

Bit 13:12

Description nco_reg_sel selects sync for loading the NCO register

0

‘00’

TXENABLE from FIFO output

0

‘01’

SYNC from FIFO output

1

‘10’

Sync_sif_sig

1

‘11’

Always 0

Setting

Bit 15:14

Description nco_sel selects sync for loading the NCO accumulator

0

‘00’

TXENABLE from FIFO output

0

‘01’

SYNC from FIFO output

1

‘10’

Sync_sif_sig

1

‘11’

Always 0

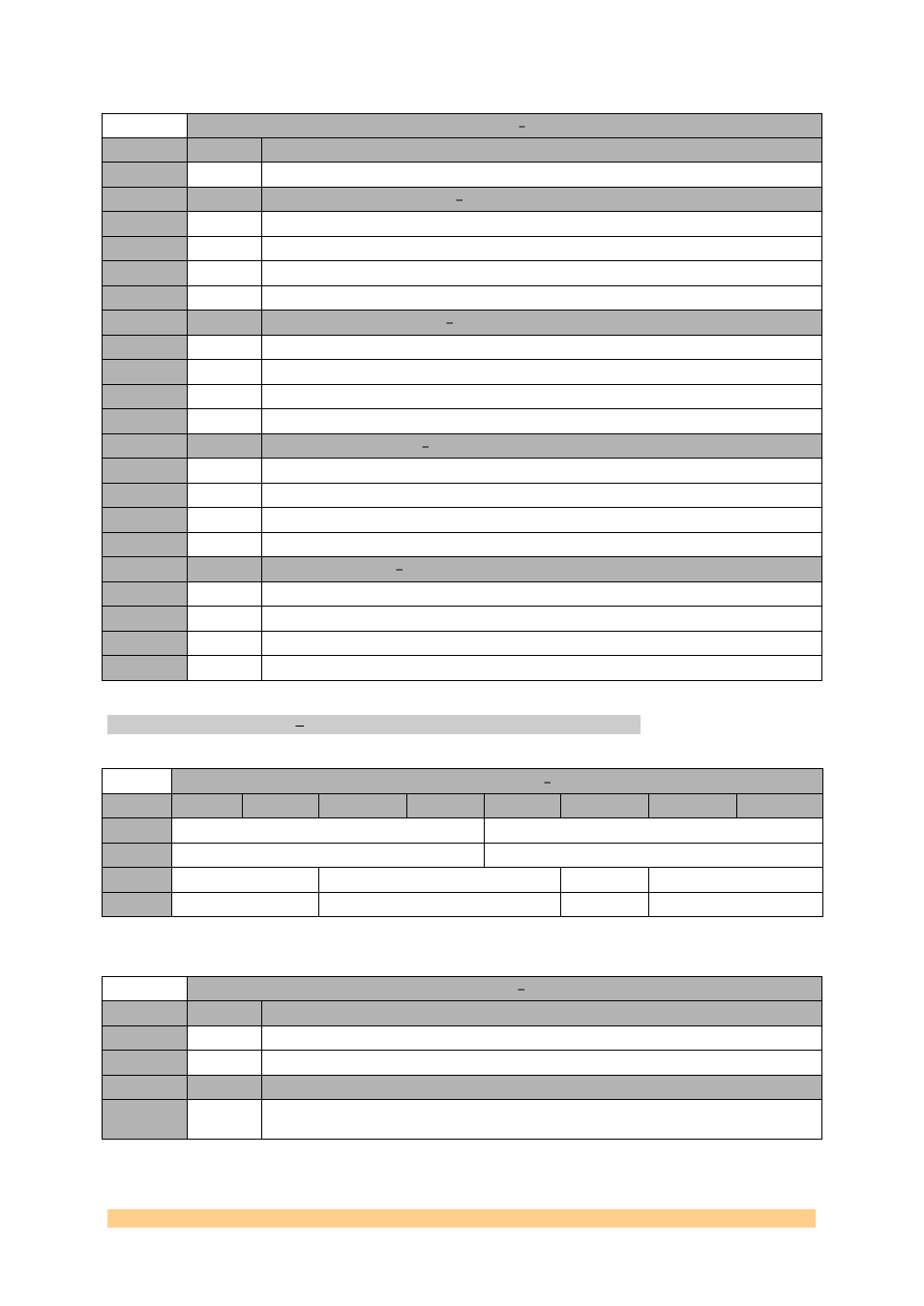

DAC Chab Register B 0x4B.

DAC Chab Register B 0x4B

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Fifo_sync_strt

Reserved

Default

‘1000’

‘0000’

0

Reserved

Fifo_sel

Aflag_sel

Reserved

Default

‘00’

‘010’

‘1’

‘00’

DAC Chab Register B 0x4B

Setting

Bit 2

Description aflag_sel

0

‘0’

The rising edge of TXENABLE is used to determine the A sample.

0

‘1’

The MSB of the inputopposite of incoming data is used to determine the A sample.

Setting

Bit 15:12

Description fifo_sync_strt

0

When the sync fifo to the fifo iccurs, this is the values loaded into the fifo output

counter.