Dac chab register b 0x3b, Dac chab register c 0x3c – Sundance SMT942 User Manual

Page 35

User Manual SMT942

Page 35 of 55

Last Edited: 23/08/2011 17:25:00

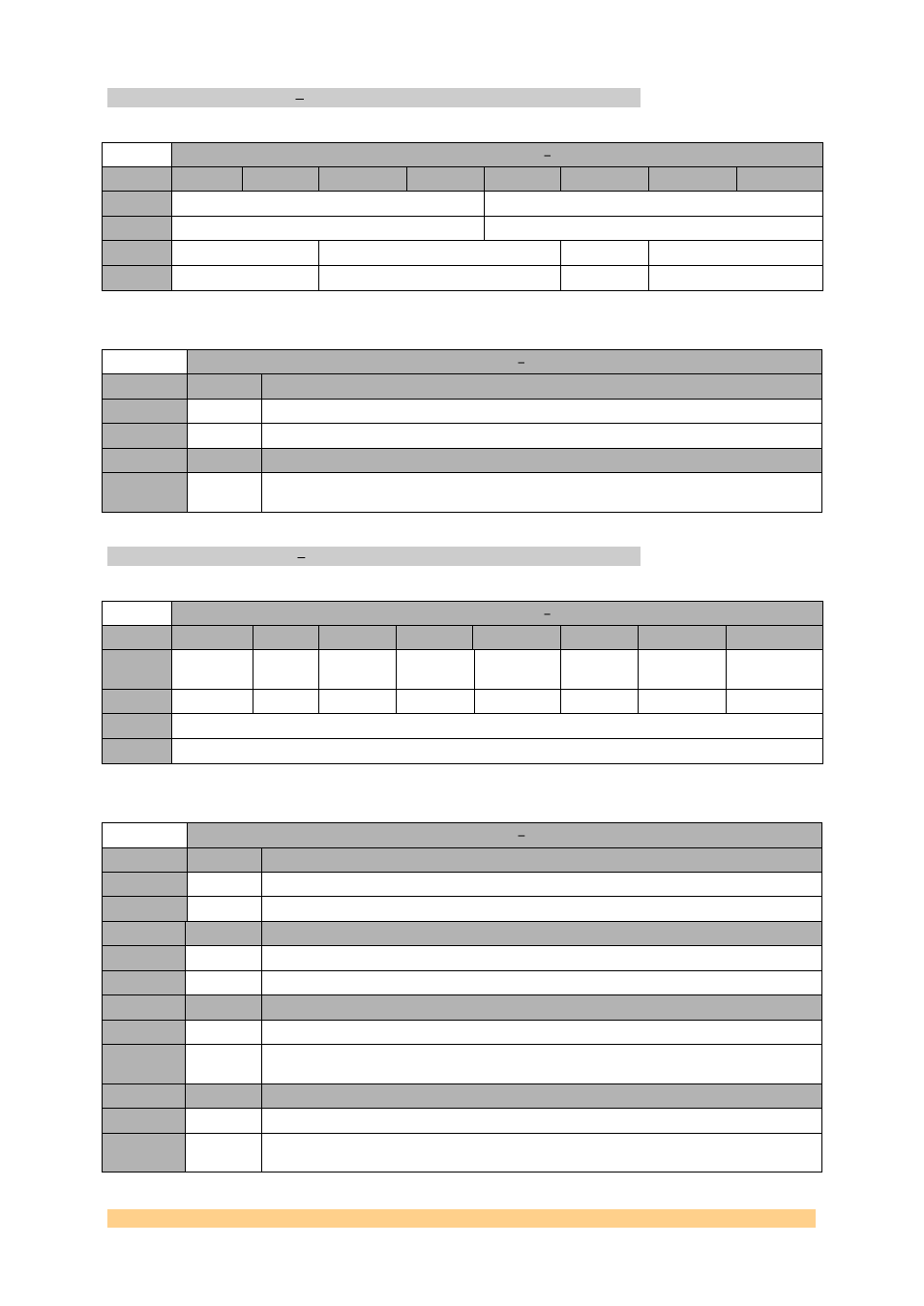

DAC Chab Register B 0x3B.

DAC Chab Register B 0x3B

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Fifo_sync_strt

Reserved

Default

‘1000’

‘0000’

0

Reserved

Fifo_sel

Aflag_sel

Reserved

Default

‘00’

‘010’

‘1’

‘00’

DAC Chab Register B 0x3B

Setting

Bit 2

Description aflag_sel

0

‘0’

The rising edge of TXENABLE is used to determine the A sample.

0

‘1’

The MSB of the inputopposite of incoming data is used to determine the A sample.

Setting

Bit 15:12

Description fifo_sync_strt

0

When the sync fifo to the fifo iccurs, this is the values loaded into the fifo output

counter.

DAC Chab Register C 0x3C.

DAC Chab Register C 0x3C

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Io_1p8_3p

3

Reserve

d

sleepb

sleepa

isbiaslpfb_

a

isbiaslpf_

b

Pll_sleep

Pll_ena

Default

‘0’

‘0’

‘0’

‘0’

‘1’

‘1’

‘0’

‘1’

0

Reserved

Default

‘00000000’

DAC Chab Register C 0x3C

Setting

Bit 8

Description pll_ena

0

‘0’

Pll is off.

1

‘1’

Pll is on and its output clock is used to clock the DAC.

Setting

Bit 9

Description pll_sleep

0

‘0’

Pll is not in sleep mode.

1

‘1’

Pll is in sleep mode.

Setting

Bit 10

Description isbiaslpf_b

0

‘0’

Low pass filter for the current source bias in DACB is off.

1

‘1’

Low pass filter for the current source bias in DACB is on. The low pass filter will set a

corner at 472Hz when low and 95KHz when high

Setting

Bit 11

Description isbiaslpfb_a

0

‘0’

Low pass filter for the current source bias in DACA is off.

1

‘1’

Low pass filter for the current source bias in DACA is on. The low pass filter will set a

corner at 472Hz when low and 95KHz when high