Dac chab register 2 0x42 – Sundance SMT942 User Manual

Page 40

User Manual SMT942

Page 40 of 55

Last Edited: 23/08/2011 17:25:00

1

1

1 clock cycles

2

2

2 clock cycles

3

3

3 clock cycles

Setting

Bit 15

Description ser_dac_data_ena

0

0

Normal mode of operation.

1

1

Muxes ser_dac_data to both DACs.

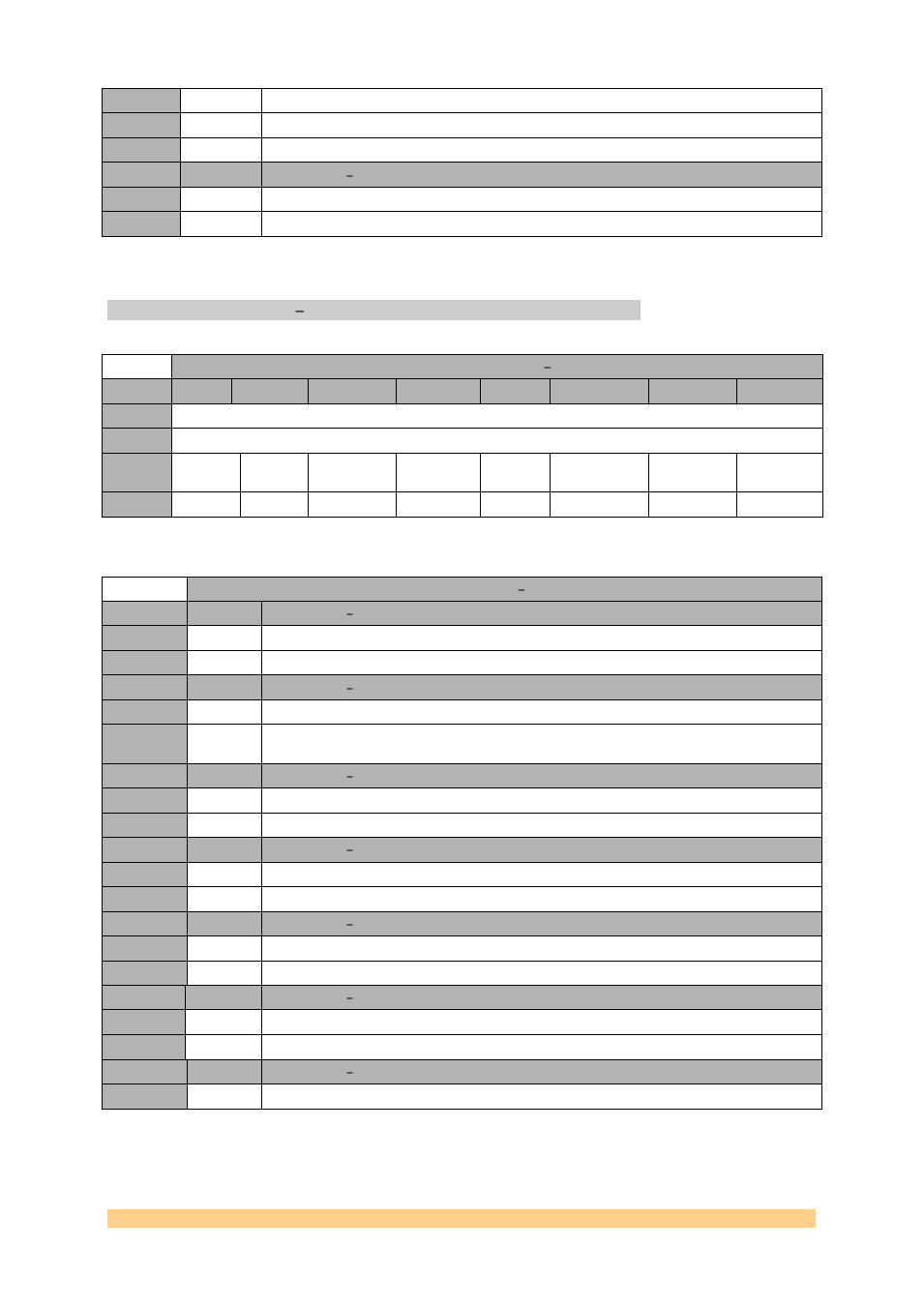

DAC Chab Register 2 0x42.

DAC Chab Register 2 0x42

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Phase Offset [7:0]

Default

‘00000000

0

Sif4

Sif_sync

_sig

Clkdiv_syn

c_ena

Clkdiv_syn

c_sel

Reserve

d

Clkdiv_shift

Mixer gain

Reserved

Default

‘0’

‘0’

‘1’

‘0’

‘0’

‘0’

‘1’

‘0’

DAC Chab Register 2 0x42

Setting

Bit 1

Description Mixer gain

0

0

Nothing added.

1

1

Adds 6dbs to the mixer gain output.

Setting

Bit 2

Description clkdiv shift

0

0

1

1

A rising edge on the selected sync for the clock dividers will cause a slip in the

synchronous counter by one period (used for multi DAC time alignement.

Setting

Bit 4

Description clkdiv sync sel

0

0

SYNC selected as input to sync clock dividers

1

1

TXENABLE selected as input to sync clock dividers

Setting

Bit 5

Description clkdiv sync ena

0

0

1

1

Enables syncing of the clock divider using the sync or TXENABLE pins

Setting

Bit 6

Description sif sync sig

0

0

Clears sync

1

1

Causes a sync

Setting

Bit 7

Description sif4

0

0

3-bit serial interface

1

1

4-bit serial interface

Setting

Bit 15:8

Description Phase Offset[7:0]

0

0