Sundance SMT942 User Manual

Page 24

User Manual SMT942

Page 24 of 55

Last Edited: 23/08/2011 17:25:00

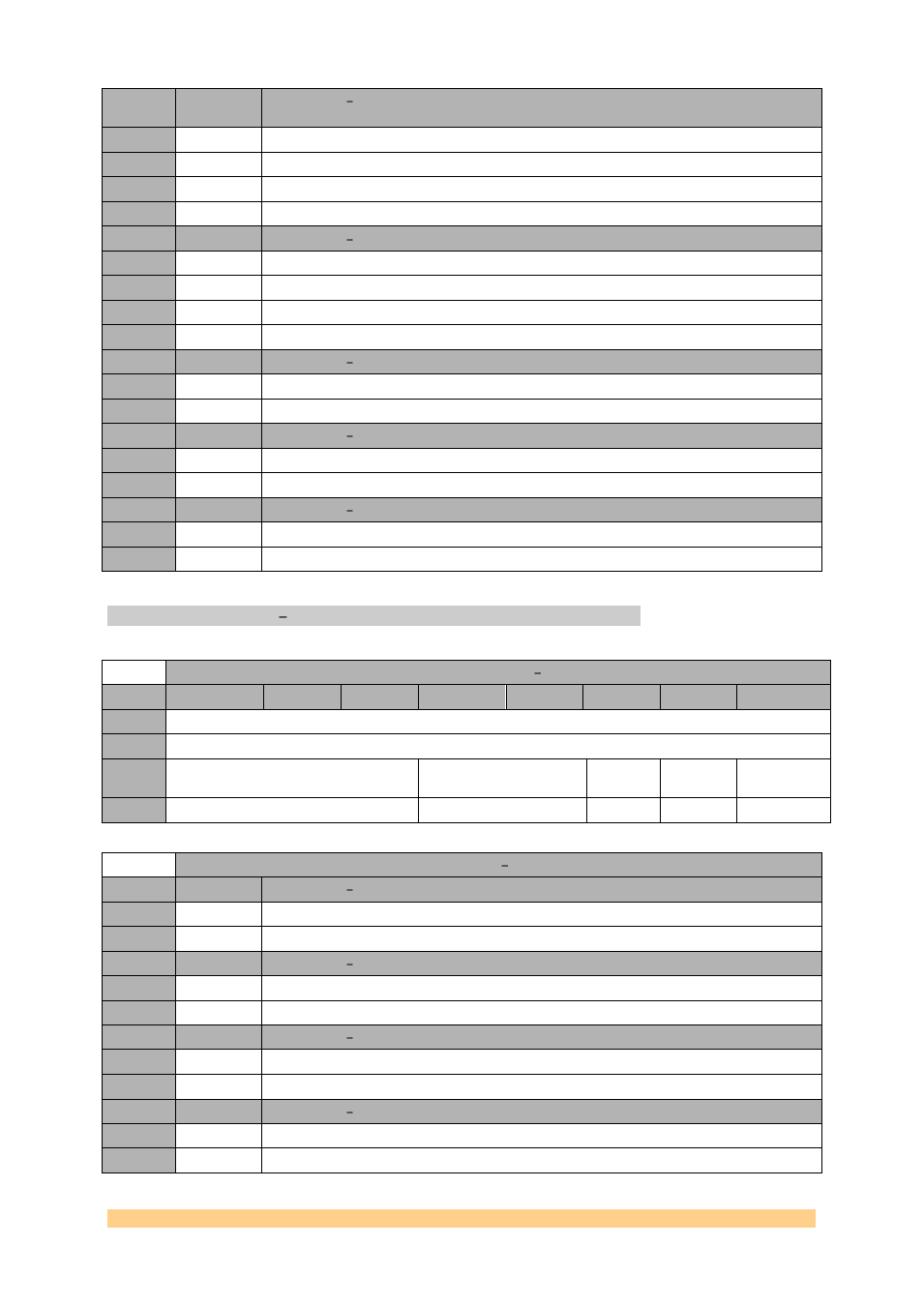

Setting

Bit 9:8

Description Hold function reactivates after a number of reference clock cycles -

HOLD_CNT

0

‘00’

64 clock cycles

1

‘01’

128 clock cycles

2

‘10’

256 clock cycles

3

‘11’

512 clock cycles

Setting

Bit 11:10

Description Extended lock detect window - LOCKW

0

‘00’

1

‘01’

2

‘10’

3

‘11’

Setting

Bit 13

Description DIVSYNC_DIS

0

‘0’

Start signal is synchronised to N/M divider input clock

1

‘1’

Setting

Bit 14

Description START_BYPASS

0

‘0’

Start signal is synchronised to VCXO clock

1

‘1’

Start synch block is bypassed

Setting

Bit 15

Description INDET_BP

0

‘0’

Synch logic active when VCXO/AUX clocks are available

1

‘1’

Synch logic is independent from VCXO/AUX

CLOCK Register 13 0x23.

Clock Register 13 0x23

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved

Default

‘00000000’

0

Reserved

BIAS_DIV_FB

NPRESET

_MDIV

LOW_FD_

FB_EN

PLL_LOCK_B

P

Default

‘000’

‘00’

‘0’

‘0’

‘0’

Reset Register 13 0x23

Setting

Bit 0

Description PLL_LOCK_BP

0

‘0’

Synch logic waits for the first PLL lock state

1

‘1’

Synch logic independent from first PLL lock state

Setting

Bit 1

Description LOW_FD_FB_EN

0

‘0’

Synch logic is independent from VCXO/DIV_FB frequency

1

‘1’

Synch logic is started for VCXO/DIV_FB > 600khz

Setting

Bit 2

Description NPRESET_MDIV

0

‘0’

M-divider uses nHOLD as NPRESET

1

‘1’

M-divider not preset by nHOLD

Setting

Bit 4:3

Description BIAS_DIV_FB

0

‘00’

No current reduction

1

‘01’

20% current reduction