Dds register 5 – step increment msb - 0x25 – Sundance SMT350 User Manual

Page 39

Version 1.9

Page 39 of 45

SMT350 User Manual

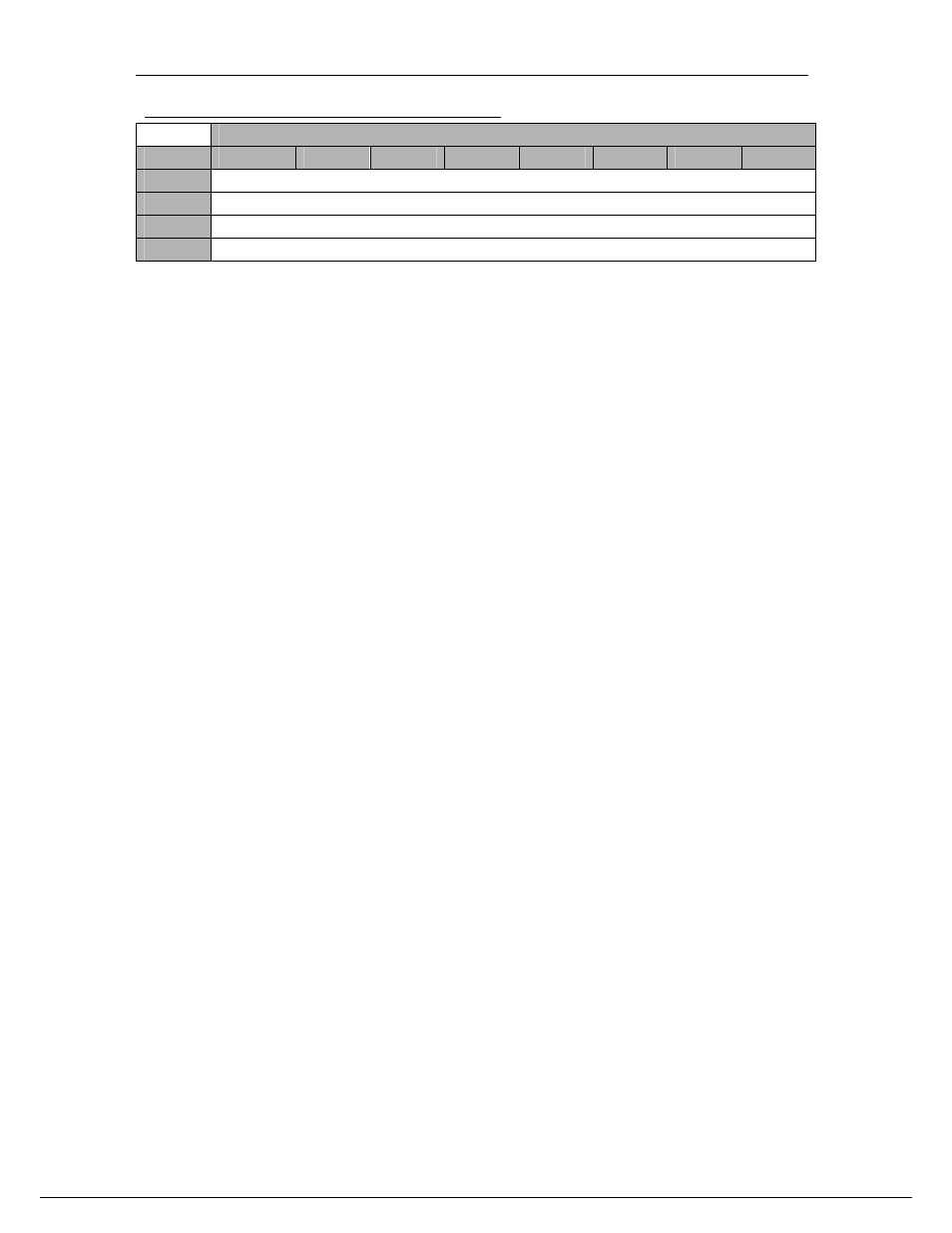

DDS Register 5 – Step Increment MSB - 0x25

DDS Register 5 – 0x25

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

DDS Step Phase Increment [31…24]

Default

‘00000000’

0

DDS Step Phase Increment [23…16]

Default

‘00000000’

The Step Phase Increment value is coded on 32 bits. It corresponds to the increment

in phase on each sampling clock cycle (Sweep Mode).

When used to generate a fixed frequency, Start Phase Increment should be equal

to Stop Phase Increment and Step Phase Increment should be equal to 1.

For Registers 0x24 and 0x25 to take effect, Bit 6 of register 0x1D must be set to 1.

DAC Channel A is the Sine output of the DDS and DAC Channel B is the Cosine

output of the DDS. Both outputs are therefore is quadrature.

- SMT107 (16 pages)

- SMT6035 v.2.2 (39 pages)

- SMT6012 v.4.6 (22 pages)

- FC100 (12 pages)

- FC108 v.1.1 (10 pages)

- SMT6065 v.4.0 (45 pages)

- FFT v.2.1 (19 pages)

- SMT111 (18 pages)

- SMT118LT (10 pages)

- SMT118 (20 pages)

- SMT123-SHB (13 pages)

- SMT128 (15 pages)

- SMT145 (18 pages)

- SMT148 (35 pages)

- SMT130 v.1.0 (46 pages)

- SMT148FX (48 pages)

- SMT310Q (55 pages)

- PARS (70 pages)

- SMT166-FMC (52 pages)

- SMT166 (44 pages)

- SMT300Q v.1.6 (61 pages)

- SMT310 v.1.6 (50 pages)

- SMT317 (24 pages)

- SMT326v2 (24 pages)

- SMT338 (19 pages)

- SMT349 (32 pages)

- SMT339 v.1.3 (27 pages)

- SMT338-VP (22 pages)

- SMT358 (25 pages)

- SMT351T (37 pages)

- SMT351 (25 pages)

- SMT362 (30 pages)

- SMT365G (23 pages)

- SMT364 (37 pages)

- SMT373 (15 pages)

- SMT368 (24 pages)

- SMT370v3 (46 pages)

- SMT377 (22 pages)

- SMT381 2007 (31 pages)

- SMT381-VP (81 pages)

- SMT387 (42 pages)

- SMT391 (18 pages)

- SMT384 (47 pages)

- SMT390-VP (55 pages)