Sundance SMT350 User Manual

Page 33

Version 1.9

Page 33 of 45

SMT350 User Manual

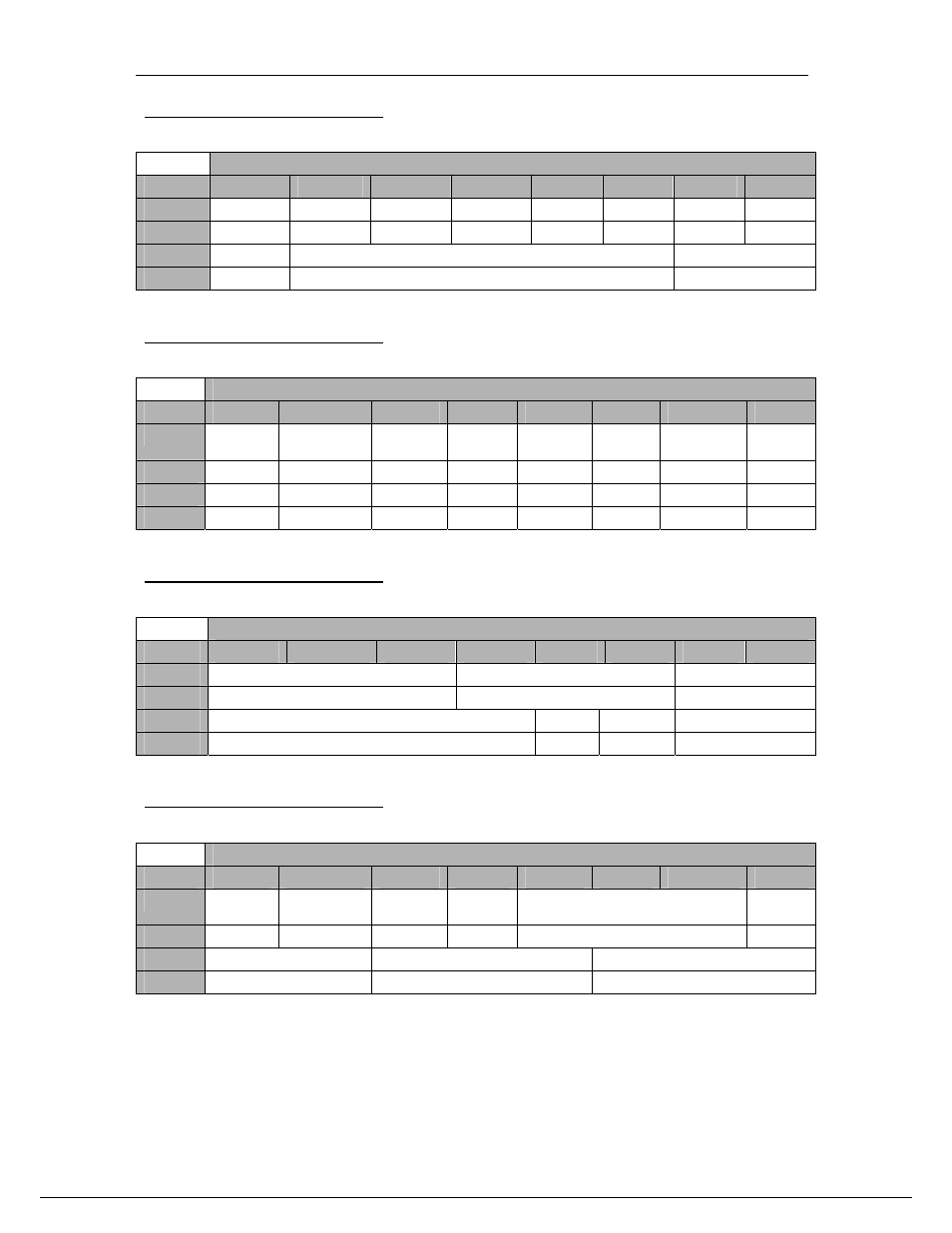

CDCM7005 Register 2 – 0x12.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 2 – 0x12

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

OUT2A0 OUT1B1 OUT1B0 OUT1A1 OUT1A0

OUT0B1

OUT0B0

OUT0A1

Default

‘0’ ‘0’ ‘0’ ‘0’ ‘0’

‘0’

‘0’

‘0’

0

OUT0A0

Output Signaling Selcetion[5:0]

Register Selection[1:0]

Default

‘0’ ‘00000’

‘01’

CDCM7005 Register 3 – 0x13.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 3– 0x13

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

90Div8 90Div4 ADClock

Status

VCXO

Status Ref

OUT4B1

OUT4B0

OUT4A1

Default

‘0’ ‘0’ ‘0’

‘0’

‘0’

‘0’ ‘0’ ‘0’

0

OUT4A0 OUT3B1 OUT3B0

OUT3A1

OUT3A0

OUT2B1 OUT2B0 OUT2A1

Default

‘0’ ‘0’ ‘0’

‘0’

‘0’

‘0’ ‘0’ ‘0’

CDCM7005 Register 4 – 0x14.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 4 – 0x14

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Y0_MUX Width

FB_MUX

Pulse

Default

‘000’ ‘000’

‘00’

0

CP Current

PRECP

CP_DIR

Register Selection[1:0]

Default

‘0000’ ‘0’

‘0’

‘10’

CDCM7005 Register 5 – 0x15.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 5– 0x15

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Hold Reset

ResHold

Power

Down

Y4_MUX Y3_MUX

Default

‘0’ ‘0’ ‘0’

‘0’

‘000’

‘0’

0

Y3_MUX Y2_MUX

Y1_MUX

Default

‘00’ ‘000’

‘000’