Sundance SMT350 User Manual

Page 15

Version 1.9

Page 15 of 45

SMT350 User Manual

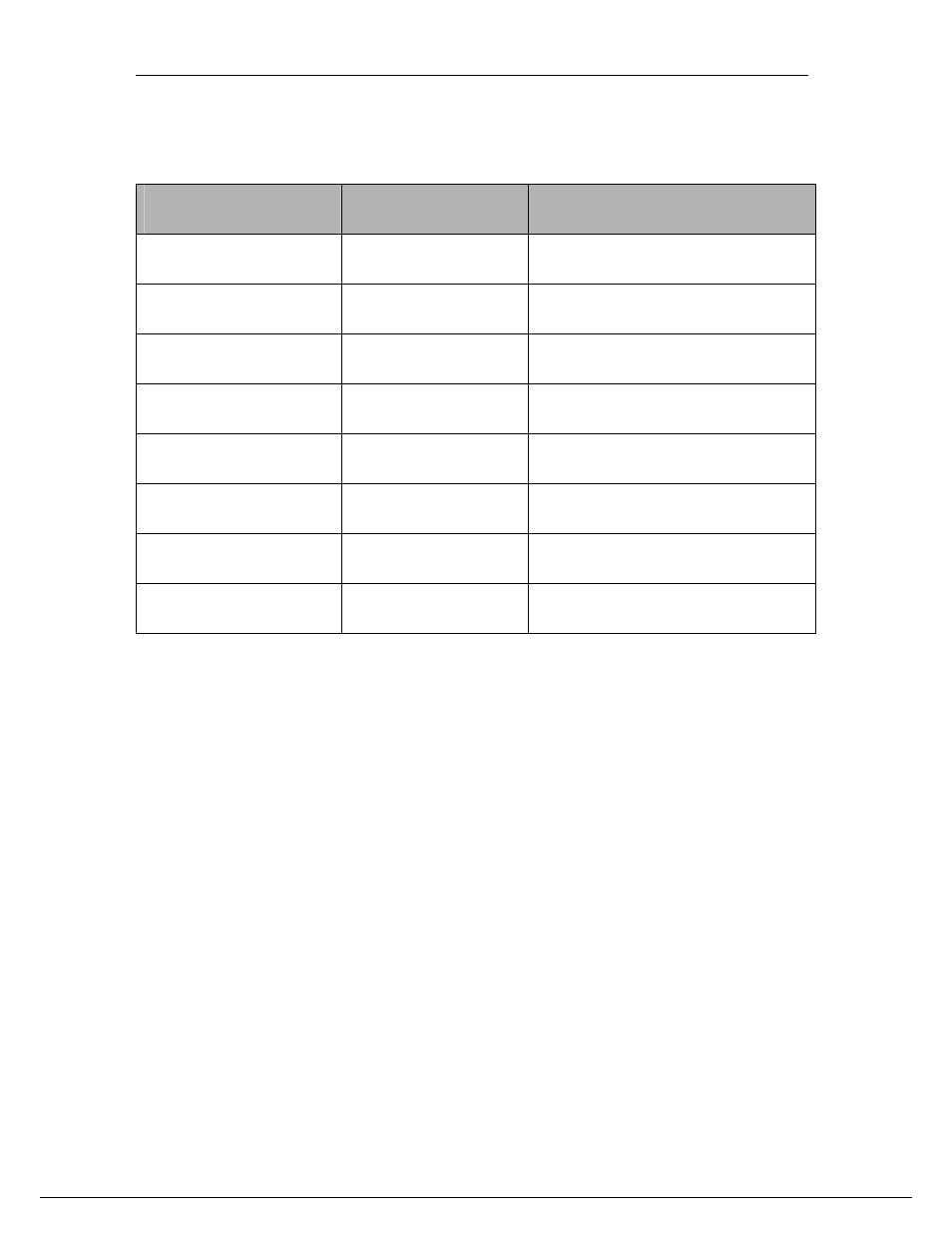

ADCs can both receive the same clock or the fraction of the CDCM7005 input clock

(/2, /3, /4, /6, /8 or /16), the maximum being 125MHz for each ADC. This input clock

can be coming from the on-board fixed VCXO or from an external source. Here is a

list of possible sampling frequencies for the ADCs:

ADC Sampling

Frequency

CDCM7005 Setting

Clock source

Not Allowed

/1 On-board

VCXO

(fixed

245.76MHz)

122.88 MHz

/2

On-board VCXO (fixed

245.76MHz)

81.92 MHz

/3

On-board VCXO (fixed

245.76MHz)

61.44 MHz

/4

On-board VCXO (fixed

245.76MHz)

40.96 MHz

/6

On-board VCXO (fixed

245.76MHz)

30.72 MHz

/8

On-board VCXO (fixed

245.76MHz)

15.36 MHz

/16

On-board VCXO (fixed

245.76MHz)

Anything between 10

and 125 MHz

/1, /2, /3, /4, /6, /8 or

/16

External Clock

The same applies to the DAC, with a maximum sampling frequency for clk1 of

160MHz and for clk2 of 500Mhz.

Below is shown how the external clock is fed to the system. By default it is single-

ended and AC-coupled before being converted into LVPECL format. The option of

having a differential external clock is still possible on the hardware by the way of

fitting or not some of the components.