Sundance SMT350 User Manual

Page 26

Version 1.9

Page 26 of 45

SMT350 User Manual

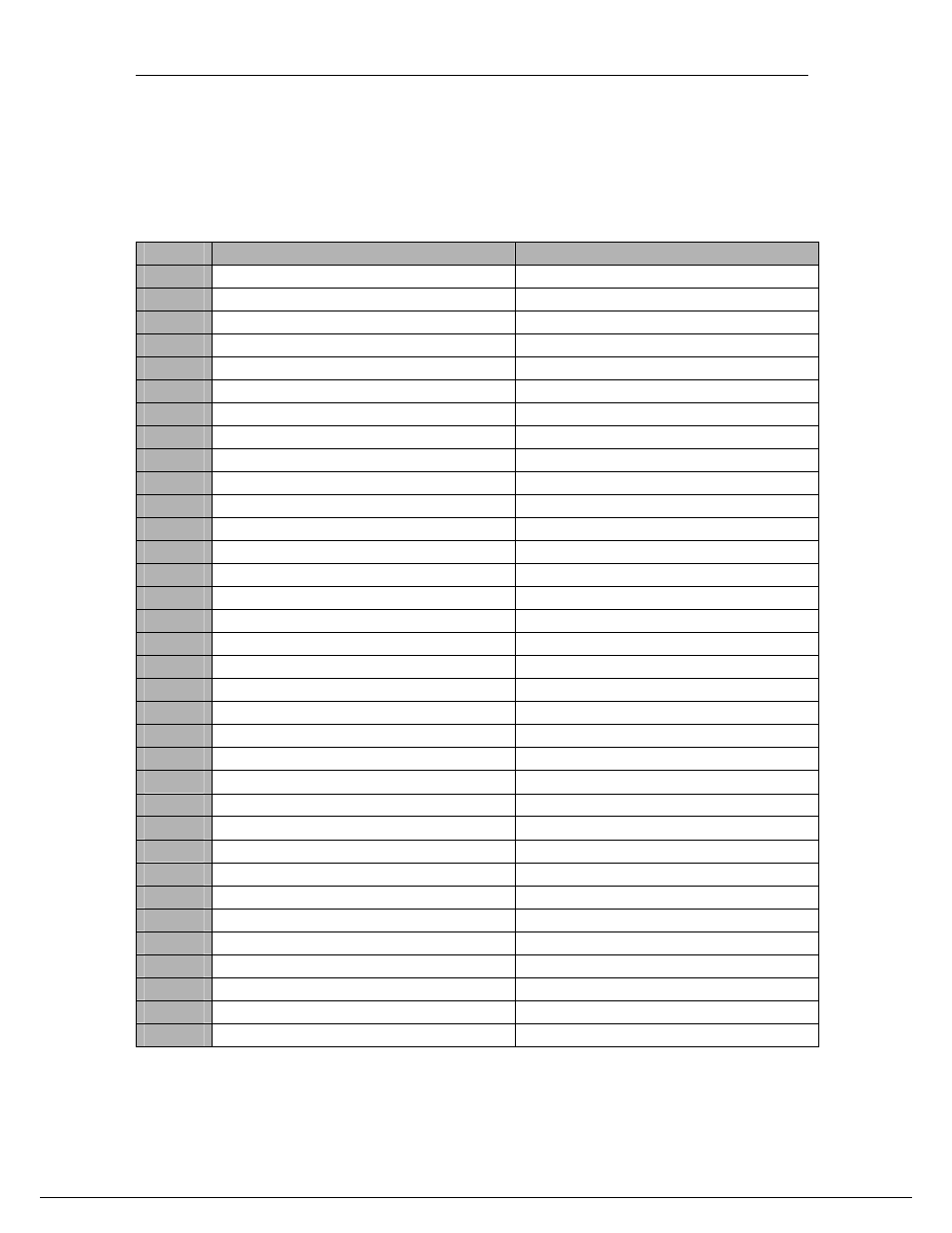

Memory Map

The write packets must contain the address where the data must be written to and

the read packets must contain the address where the required data must be read.

The following figure shows the memory map for the writable and readable Control

Registers on the SMT350:

Address

Writable Registers

Readable Registers

0x00

Reset Register.

Reserved.

0x01

Test Register.

Test Register.

0x02

ADCA Register 0.

Read-back (FPGA Register) ADCA Register 0.

0x03

ADCA Register 1.

Read-back (FPGA Register) ADCA Register 1.

0x04

ADCA Register 2.

Read-back (FPGA Register) ADCA Register 2.

0x05

ADCB Register 0.

Read-back (FPGA Register) ADCB Register 0.

0x06

ADCB Register 1.

Read-back (FPGA Register) ADCB Register 1.

0x07

ADCB Register 2.

Read-back (FPGA Register) ADCB Register 2.

0x08

DAC Register 0.

Read-back (FPGA Register) DAC Register 0.

0x09

DAC Register 1.

Read-back (FPGA Register) DAC Register 1.

0x0A

DAC Register 2.

Read-back (FPGA Register) DAC Register 2.

0x0B

DAC Register 3.

Read-back (FPGA Register) DAC Register 3.

0x0C

DAC Register 4.

Read-back (FPGA Register) DAC Register 4.

0x0D

DAC Register 5.

Read-back (FPGA Register) DAC Register 5.

0x0E

DAC Register 6.

Read-back (FPGA Register) DAC Register 6.

0x0F

DAC Register 7.

Read-back (FPGA Register) DAC Register 7.

0x10

CDCM7005 Register 0.

Read-back (FPGA Register) CDCM7005 Register 0.

0x11

CDCM7005 Register 1.

Read-back (FPGA Register) CDCM7005 Register 1.

0x12

CDCM7005 Register 2.

Read-back (FPGA Register) CDCM7005 Register 2.

0x13

CDCM7005 Register 3.

Read-back (FPGA Register) CDCM7005 Register 3.

0x14

CDCM7005 Register 4.

Read-back (FPGA Register) CDCM7005 Register 4.

0x15

CDCM7005 Register 5.

Read-back (FPGA Register) CDCM7005 Register 5.

0x16

CDCM7005 Register 6.

Read-back (FPGA Register) CDCM7005 Register 6.

0x17

CDCM7005 Register 7.

Read-back (FPGA Register) CDCM7005 Register 7.

0x18

Reserved

Main Module Temperature

0x19

Reserved

Main Module FPGA Temperature

0x1A

Reserved

Mezzanine Module Temperature

0x1B

Reserved

Mezzanine Module Converter Temperature

0x1C

Misc Register (Trigger, Clock Selection, etc…).

Read-back Misc Register.

0x1D

Update and Read-back command Register

Firmware Version and Status bits.

0x20

DDS Register 0 – Start Phase Increment LSB

Read-back (FPGA Register) DDS Register 0.

0x21

DDS Register 1 – Start Phase Increment MSB

Read-back (FPGA Register) DDS Register 1.

0x22

DDS Register 2 – Stop Phase Increment LSB

Read-back (FPGA Register) DDS Register 2.

0x23

DDS Register 3 – Stop Phase Increment MSB

Read-back (FPGA Register) DDS Register 3.