Bank a bank b bank c, Bank b – Sundance SMT350 User Manual

Page 22

Version 1.9

Page 22 of 45

SMT350 User Manual

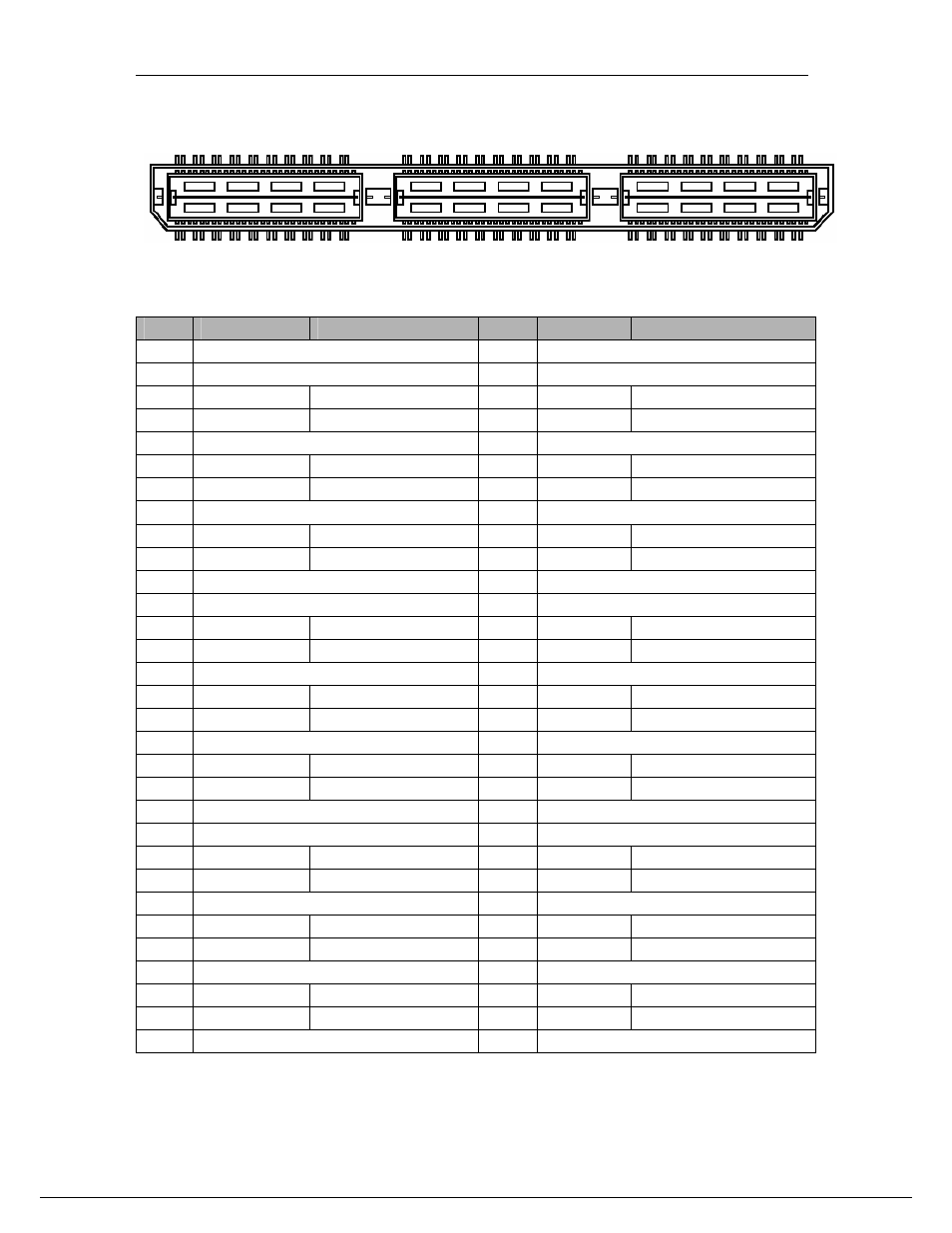

Bank

A Bank

B Bank

C

1 3 5 7

41 43

81 83

2 4 6 8

Bank B

Pin No

Pin Name

Signal Description

Pin No

Pin Name

Signal Description

Type

Clock and Trigger System Signals

Type

Clock and Trigger System Signals

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

41

SMBClk

Temperature Sensor Clock.

42

SMBData

Temperature Sensor Data.

43 SMBnAlert

Temperature

Sensor

Alert.

44 SerialNo Reserved

Dir

Daughter Card to Main Module

Dir

Reserved

45 AdcVDacI

Reserved

46 AdcVDacQ

Reserved

47 AdcVRes

Reserved

48 AdcReset Reserved

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

49 D3v3Enable Reserved

50 D2v5Enable

Reserved

51

AdcMode

ADCA Serial Clock.

52

AdcClock

ADCA Serial Data.

Type

ADC Specific Signals

Type ADC

Specific

Signals

Dir

Main Module to Daughter Card

Dir

Reserved

53

AdcLoad

ADCA Serial Enable.

54

AdcData

ADCB Serial Clock.

55

AdcCal

ADCB Serial Data.

56

AdjClkCntr0

ADCB Serial Enable.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

57

AdjClkCntr1

ADCs Format (binary, 2’s)

58

AdjClkCntr2

ADCs Reset

59

AdjClkCntr3

ADCs Output Enable

60

PllCntr0

CDCM7005 serial Enable.

Dir

Daughter Card to Main Module

Dir

Daughter Card to Main Module

61

PllCntr1

CDCM7005 serial Clock.

62

PllCntr2

CDCM7005 serial Data.

63

PllCntr3

CDCM7005 Clock Selection.

64

AdcAClkSel

DAC PhStr.

Type

Module Control Signals

Type

Module Control Signals

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

65

AdcBClkSel

DAC Reset.

66

IntClkDivEn

DAC Pll Lock.

67

IntClkDivnReset

DAC Serial Enable.

68

IntExtClkDivEn DAC Serial Clock.

Dir

Main Module to Daughter Card

Dir

Main Module to Daughter Card

69

IntExtClkDivnReset DAC Serial Data.

70

FpgaVRef

Reserved

71 FpgaTck

Reserved

72 FpgaTms Reserved

Dir

Daughter Card to Main Module

Dir

Reserved

73 FpgaTdi

Reserved

74 FpgaTdo Reserved

75 MspVRef

Reserved

76 MspTck Reserved

Dir

Daughter Card to Main Module

Dir

Reserved