Sundance SMT350 User Manual

Page 32

Version 1.9

Page 32 of 45

SMT350 User Manual

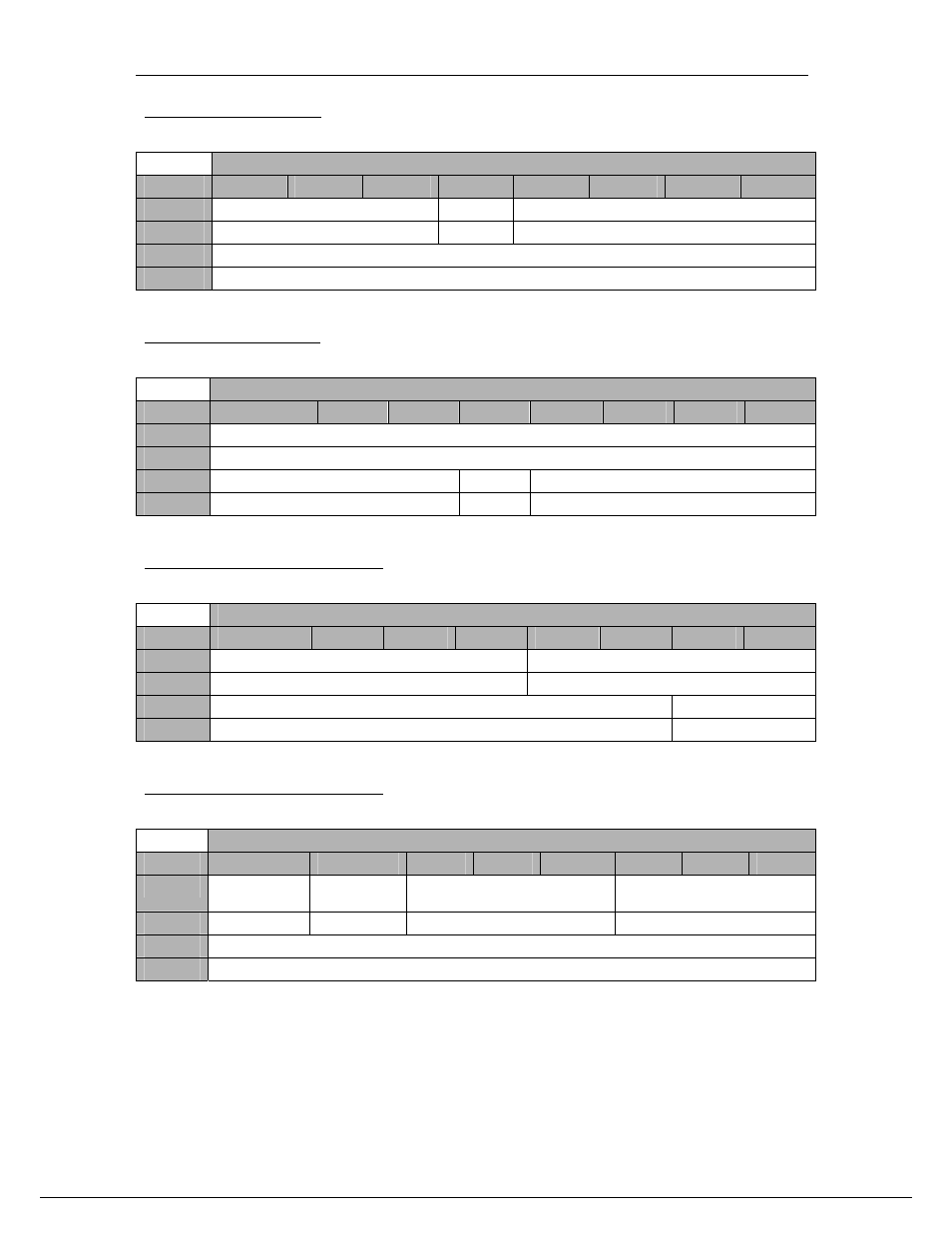

DAC Register 6 – 0xE.

For more details, refer to DAC5686 datasheet.

DAC Register 6 – 0xE

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Daca_offset[10:8] sleepa

Daca_gain[11:8]

Default

‘0’

‘0000’

1

Dacb_offset[7:0]

Default

‘00000000’

DAC Register 7 – 0xF.

For more details, refer to DAC5686 datasheet.

DAC Register 7 – 0xF

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Dacb_gain[7:0]

Default

‘00000000’

1

Dacb_offset[10:8] sleepb

Dacb_gain[11:8]

Default

‘000’ ‘0’

‘0000’

CDCM7005 Register 0 – 0x10.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 0 – 0x10

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

VCXO_divider[3:0] Reference

Divider[9:6]

Default

‘0000’ ‘0000’

0

Reference Divider[5:0]

Register Selection[1:0]

Default

‘000000’ ‘00’

CDCM7005 Register 1 – 0x11.

For more details, refer to CDCM7005 datasheet.

CDCM7005 Register 1 – 0x11

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Freq Detect

Manual or Auto

Ref.

Programmable Delay N[2:0]

Programmable Delay M[2:0]

Default

‘0’ ‘0’

‘000’

‘000’

0

VCXO_divider[11:4]

Default

‘00000000’