Sundance SMT350 User Manual

Page 31

Version 1.9

Page 31 of 45

SMT350 User Manual

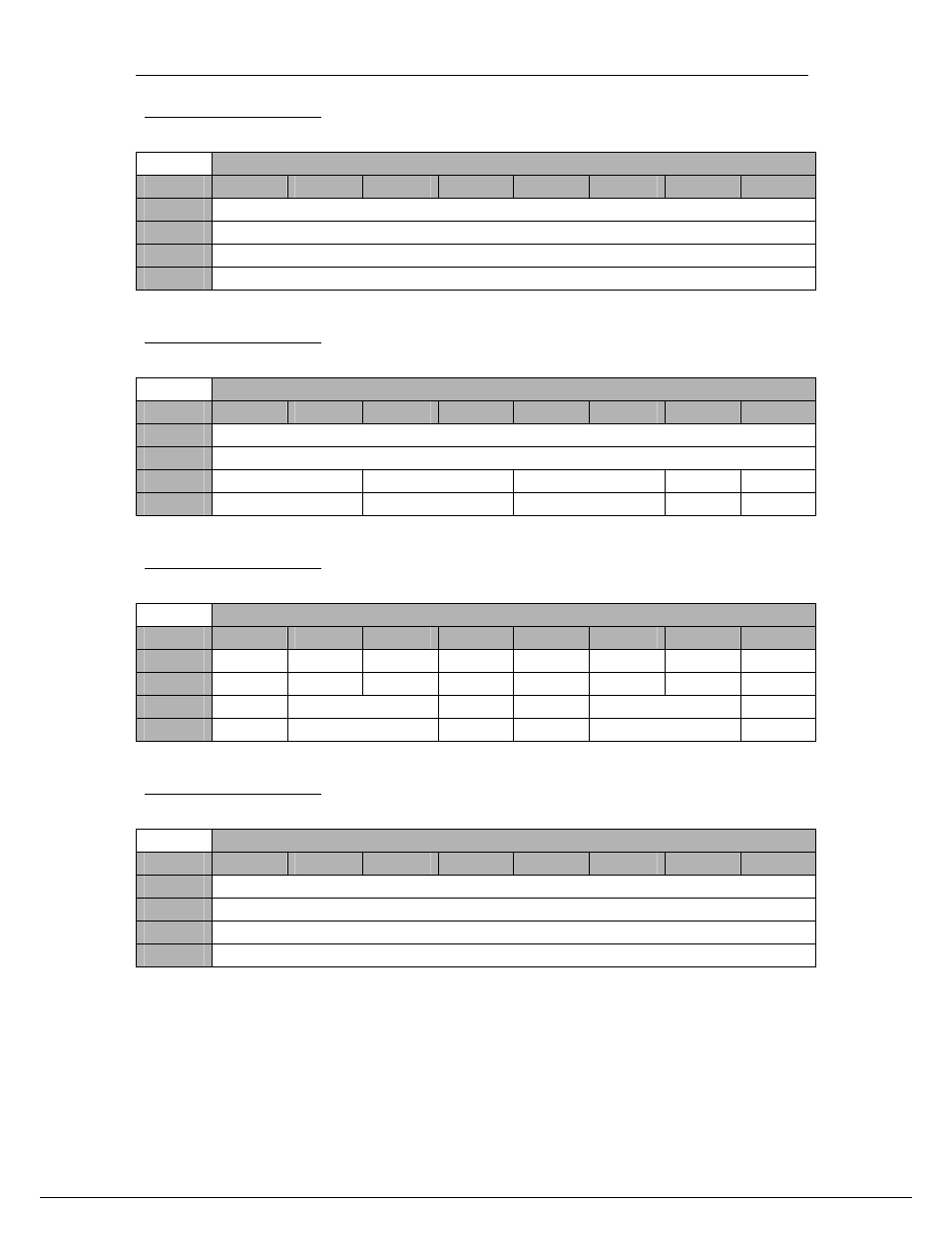

DAC Register 2 – 0xA.

For more details, refer to DAC5686 datasheet.

DAC Register 2 – 0xA

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Freq_int[31:24]

Default

‘00000000’

1

Phase_int[7:0]

Default

‘00000000’

DAC Register 3 – 0xB.

For more details, refer to DAC5686 datasheet.

DAC Register 3 – 0xB

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Phase _int[15:8]

Default

‘00000000’

1

Mode[1:0] Div[1:0] Sel[1:0]

Counter

Full

bypass

Default

‘00’ ‘00’ ‘00’

‘0’

‘0’

DAC Register 4 – 0xC.

For more details, refer to DAC5686 datasheet.

DAC Register 4 – 0xC

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Ssb

Interl

Sinc

Dith Sync

Phstr Nco

Sif4

Twos

Default

‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’ ‘0’

1

Dual_clk DSS_gain[1:0] Rspect

Qflag

Pll_rng[1:0] Rev_bus

Default

‘0’ ‘00’ ‘0’

‘0’ ‘00’ ‘0’

DAC Register 5 – 0xD.

For more details, refer to DAC5686 datasheet.

DAC Register 5 – 0xD

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

0

Daca_offset[7:0]

Default

‘00000000’

1

Daca_gain[7:0]

Default

‘00000000’