Input sequencer, Triggering – Measurement Computing LGR-5320 Series User Manual

Page 31

LGR-5320 Series User's Guide

Specifications

31

Input sequencer

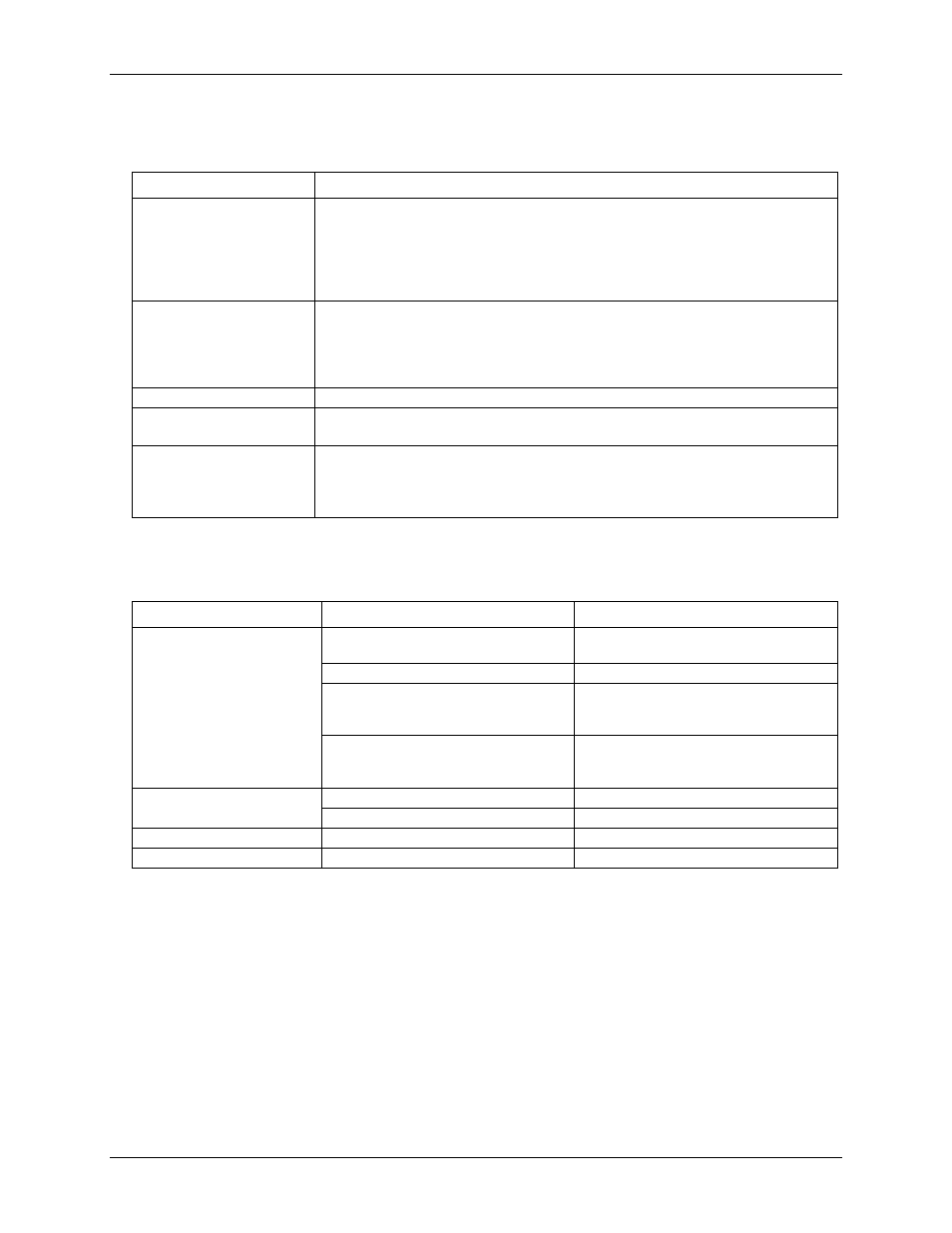

Table 4. Input sequencer specifications

Parameter

Specifications

Pacer clock sources: two

Internal

LGR-5325: 10 µs to 85.9 sec in 20 ns steps

LGR-5327/5329: 5 µs to 85.9 sec in 20 ns steps

External (PACER)

LGR-5325: 10 µs min

LGR-5327/5329: 5 µs min

Programmable parameters

per scan

Channel type (DIFF analog, single ended analog, counter, digital input)

Channel number (random order)

Gain

Any channel specified with a ±30 V range (LGR-5327/5329 only) cannot be specified

with any other range in the sequence

Depth

512 locations

Pacer interval

LGR-5325: 10 µs min (100 kHz max pacer rate)

LGR-5327/5329: 5 µs min (200 kHz max pacer rate)

Channel to channel sampling

period (scan clock)

LGR-5325: 10 µs, fixed (analog inputs)

LGR-5327/5329: 5 µs , fixed (analog inputs)

All specified digital channels (counters, digital inputs) are sampled simultaneously at the

beginning of the pacer interval

Triggering

Table 5. Triggering specifications

Parameter

Condition

Specification

Mode

External digital through DTRIG (pin 76)

Software configurable for rising or falling

edge.

External analog through ATRIG (pin 78)

Multi-channel analog (

LGR-5327/5329 only)

Level-sensitive based on acquired data. Up

to 16 channels may be used as independent

trigger sources.

Digital pattern trigger

(LGR-5327/5329 only)

Trigger when a user-defined 1 to 16 bit

digital pattern is matched on the DIN0–

DIN15 pins. Programmable mask bits.

External digital trigger latency

Non-pretrigger acquisition

100 ns typ, 1 µs max

Pretrigger acquisition

1 scan period max

External trigger pulse width

1 µs min

Internal trigger latency

2 * (1/per-channel sample rate)