External analog trigger (single-channel), Multichannel trigger (lgr-5327 and lgr-5329 only) – Measurement Computing LGR-5320 Series User Manual

Page 17

LGR-5320 Series User's Guide

Functional Details

17

If the LGR-5320 Series device is not ready due to one of the following reasons, the trigger is ignored:

Incomplete configuration

The device is finishing the previously triggered acquisition

LGR-5320 Series devices do not indicate when a trigger is ignored.

External analog trigger (single-channel)

The input signal on the

ATRIG

terminal is compared to a programmable analog trigger level.

If the analog input trigger condition is met, the LGR-5320 Series device generates an internal trigger signal.

If the device is ready for a trigger, then the trigger event occurs.

If the device is not ready—due to incomplete configuration, or because the device is finishing the

previously triggered acquisition—the trigger is ignored.

LGR-5320 Series devices do not indicate when a trigger is ignored.

Hysteresis

—The analog trigger circuit has hysteresis to reduce the occurrence of false triggering due to input

noise.

Hysteresis is the range that a signal must pass through before a trigger is generated. This prevents false triggers

from happening when small amounts of noise exist on the signal.

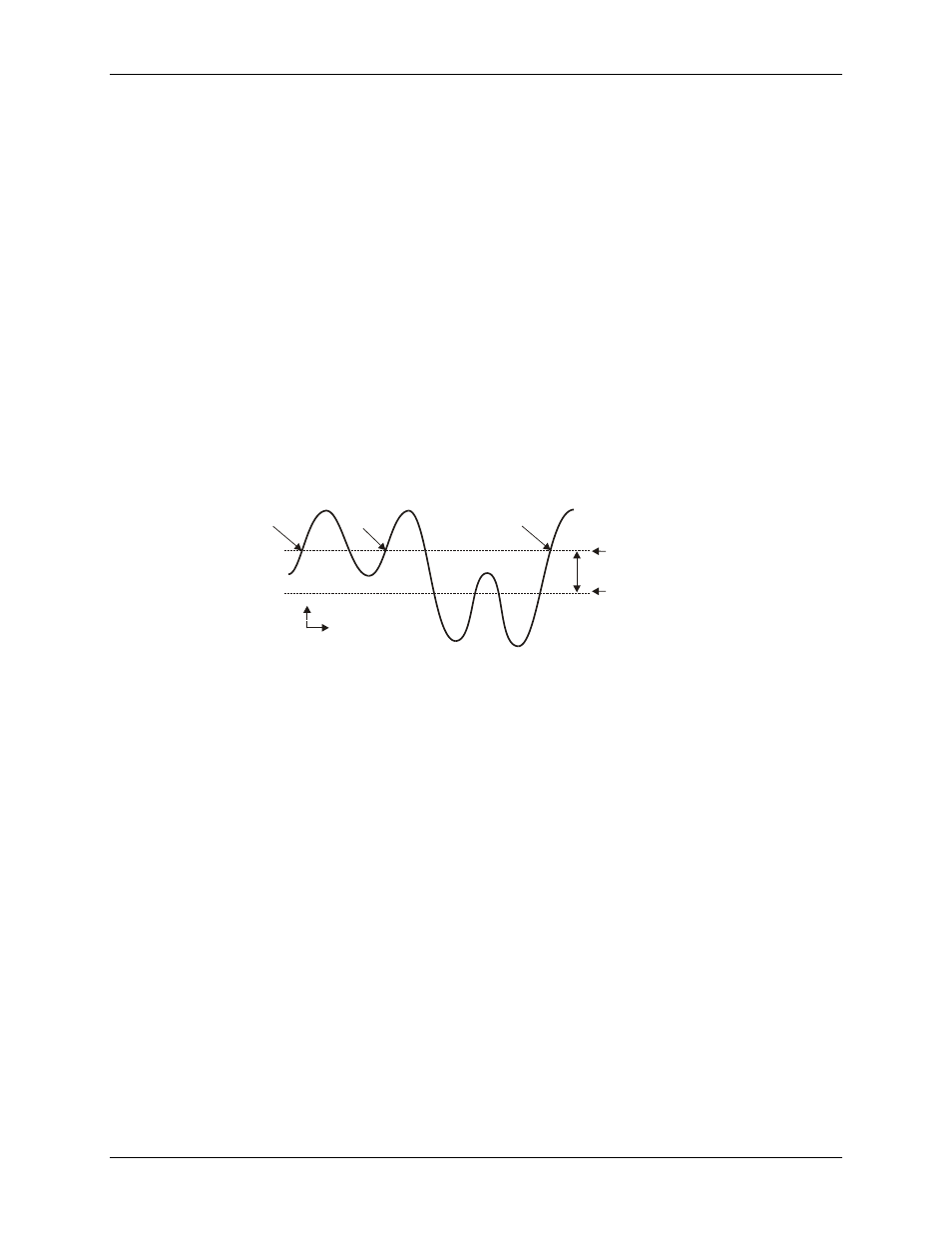

Figure 10 shows the hysteresis effect for a rising-edge trigger.

Figure 10. Hysteresis effect on a rising-edge trigger

A trigger occurs when the analog input rises above the trigger level, or threshold –but only after the input level

has been below the hysteresis range. If the level briefly drops just below the threshold—perhaps due to noise –

and then rises above it again, no trigger occurs, since the signal did not drop below the hysteresis range.

After the level drops below hysteresis, it can then produce a trigger by rising above the threshold.

Multichannel trigger (LGR-5327 and LGR-5329 only)

A multichannel trigger event is a combination of measured channel values.

The FPGA samples the specified channels, and if programmable conditions are met, triggers the acquisition.

Multichannel triggering examines digitized data, and the trigger latencies are much greater than the external

analog and digital triggers.

If minimum trigger latency is not critical in your application, you may be able to take advantage of

multichannel triggering.

The FPGA looks at (scans) digitized input channels and examines each one to determine if it meets

programmed levels for a valid trigger. This multichannel triggering is a two-step process:

1. The FPGA examines each of its specified input signals to determine if the trigger is valid.

2. After all of the channels have been examined, the FPGA logically combines the individual triggers to

generate the actual trigger. You can program the FPGA to generate a trigger if any individual trigger is

valid (OR) or if all triggers are valid (AND) (see Figure 11)

Trigger

No

Trigger

No

Trigger

Threshold Level

Hysteresis Range

Amplitude

Time

Hysteresis Level