Connector 2 connector 1, Place near ez80 output (phi) – Zilog EZ80L92 User Manual

Page 76

UM012913-0407

Schematic

Diagrams

eZ80L92 Development Kit

User Manual

72

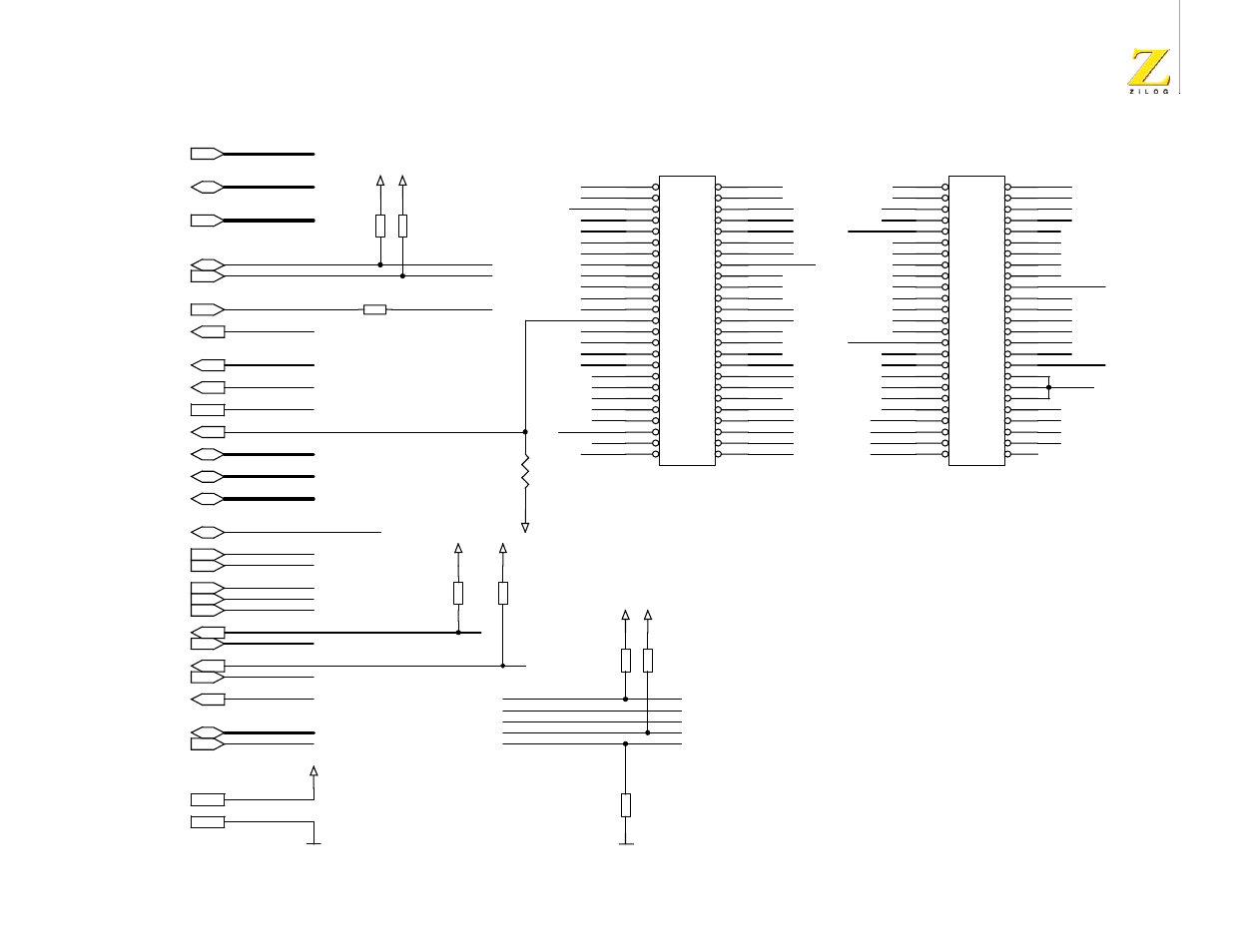

Figure 28. eZ80L92 Module Schematic Diagram, #7 of 9—Headers

place near eZ80

output (PHI)

=

=

=

=

(JTAG0 =)

connector 2

connector 1

CLK_OUT

RTC_VDD

A[0..23]

EZ80CLK

IICSDA

IICSDA

IICSCL

IICSCL

D[0..7]

-FLASHWE

-CS[0..3]

-DIS_FL

-DIS_IRDA

PB[0..7]

PC[0..7]

PD[0..7]

-RD

-WR

-IOREQ

-INSTRD

-HALT_SLP

-BUSREQ

-BUSREQ

-BUSACK

-NMI

JTAG[1..4]

-RESET

V3.3_EXT

JTAG4

TMS

TDO

JTAG1

TDI

JTAG3

TCK

JTAG2

TRIGOUT

PB1

PB3

PB5

PB7

PC1

PC3

PC5

PC7

GND_EXT

PD1

PD3

PD5

PD7

-DIS_IRDA

-CS3

EZ80CLK

V3.3_EXT

-FLASHWE

-NMI

-WAIT

GND_EXT

A0

A2

A4

A6

A8

A10

-CS2

PB0

PB2

PB4

PB6

GND_EXT

PC2

PC4

RTC_VDD

PD0

PD2

PD4

PD6

GND_EXT

IICSCL

IICSDA

TDI

TDO

TRIGOUT

TCK

TMS

-RESET

-MREQ

TDO

D3

A17

A5

V3.3_EXT

GND_EXT

A7

A22

A1

A18

A16

GND_EXT

-RD

D5

GND_EXT

A9

A23

-CS1

A13

A11

GND_EXT

D0

A19

D6

-BUSACK

V3.3_EXT

-CS0

-INSTRD

A15

D1

A14

A3

D4

D7

-IOREQ

A21

GND_EXT

-MREQ

A12

A20

-DIS_FL

-BUSREQ

-WR

D2

GND_EXT

-HALT_SLP

V3.3_EXT

PC6

PC0

-WAIT

-WAIT

DIS_ETH

V3.3

GND

R9

33

R8

4k7

R7

4k7

R12

10k

R11

10k

R13

4k7

R10

2k2

0603

R36

10K

JP1

HEADER 25X2

IDC50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

JP2

HEADER 25X2

IDC50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

R33

2k2

0603

V3.3_EXT

A[0..23]

CLK_OUT

-RESET

RTC_VDD

IICSDA

IICSCL

D[0..7]

-FLASHWE

-CS[0..3]

-DIS_FL

-DIS_IRDA

PB[0..7]

PC[0..7]

PD[0..7]

-RD

-WR

-IOREQ

-INSTRD

-HALT_SLP

-BUSACK

-WAIT

-BUSREQ

-NMI

JTAG[1..4]

GND_EXT

-MREQ

TDO

-DIS_ETH