Ez80l92 module, The part – Zilog EZ80L92 User Manual

Page 70

UM012913-0407

Schematic

Diagrams

eZ80L92 Development Kit

User Manual

66

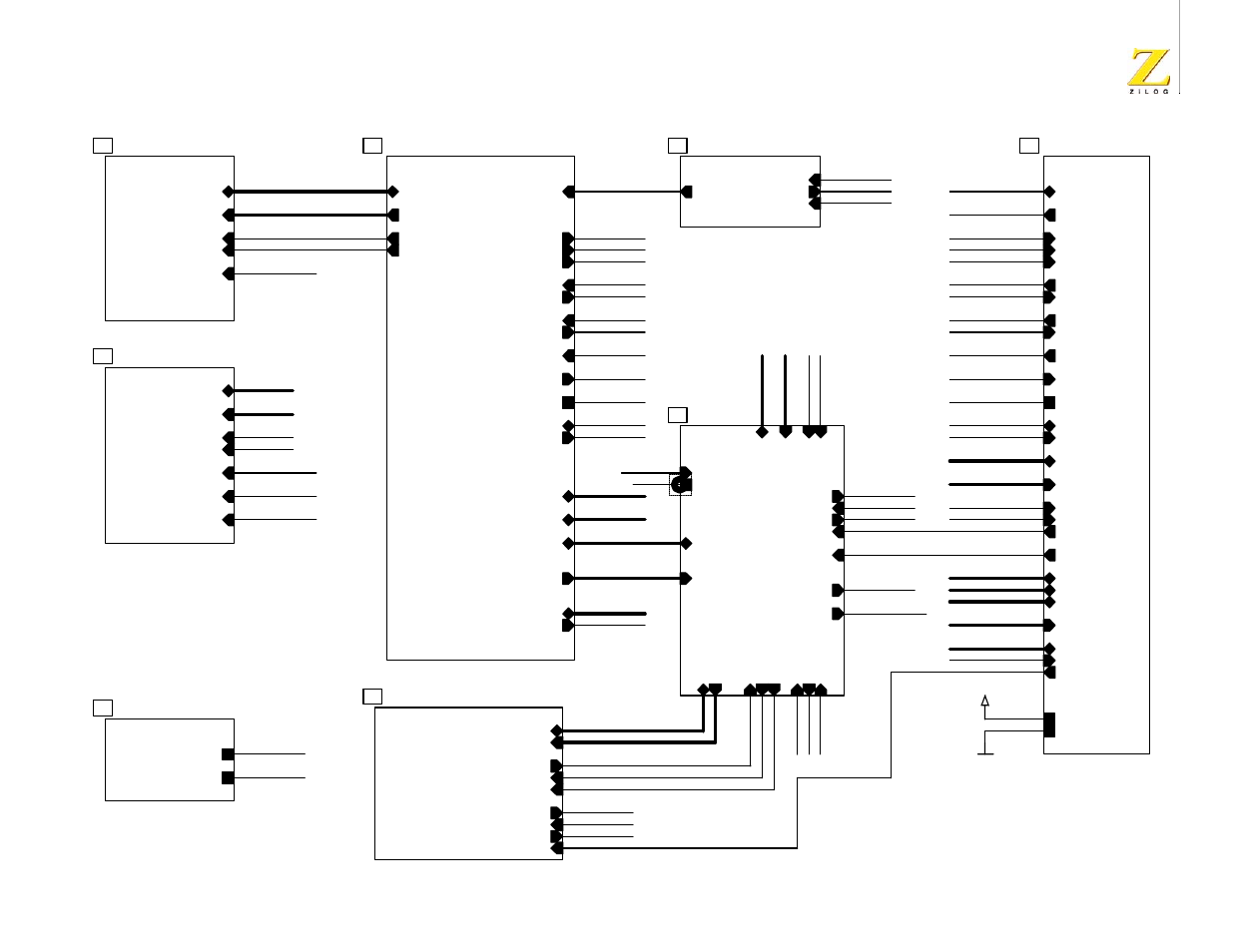

eZ80L92 Module

through

illustrate the layout of the eZ80L92 Module.

Figure 22. eZ80L92 Module Schematic Diagram, #1 of 9—Top Level

07

09

03

04

08

05

02

06

Ethernet

CS8900A

SD[0..7]

-ETHRD

-ETHWR

-SLEEP

-ACTIVE

ETHIRQ

SA[0..3]

IOCHRDY

-DIS_ETH

Connector

Headers

RTC_VDD

V3.3_EXT

GND_EXT

D[0..7]

CLK_OUT

-RESET

IICSDA

IICSCL

A[0..23]

-FLASHWE

PB[0..7]

PC[0..7]

PD[0..7]

-CS[0..3]

-DIS_IRDA

JTAG[1..4]

-RD

-WR

-IOREQ

-MREQ

-INSTRD

-WAIT

-HALT_SLP

-BUSACK

-BUSREQ

-NMI

TDO

-DIS_FL

-DIS_ETH

CPU

eZ80

D[0..7]

A[0..23]

-RD

-WR

IICSDA

IICSCL

-RESET

CLK_OUT

-BUSREQ

-BUSACK

-IOREQ

-MREQ

-INSTRD

-WAIT

-HALT_SLP

-NMI

PB[0..7]

PC[0..7]

PD[0..7]

JTAG[1..4]

-CS[0..3]

RTC_VDD

TDO

Power

PowerSupply

GND

V3.3

ROM

NOR-Flash

D[0..7]

A[0..23]

-RD

-WR

-CSFLASH

-RESFLASH

-FLASHWE

Peripherals

Reset

-RESET

IRDA_TXD

IRDA_RXD

IRDA_SD

Logic

CTRL-Logic

-RD

-WR

-ETHRD -ETH

WR

D[0..7]

SD[0..7]

A[0..23]

SA[0..3]

ETH

IRQ

-SLEE

P

-ACT

IVE

-DIS_IRDA

IRDA_SD

IRDA_TXD

IRDA_RXD

-CSFLASH

-RESFLASH

PD[0..7]

-CS[0..3]

-RESET

-DIS_FL

IOCHRDY

-WAIT

RAM

SRAM

D[0..7]

A[0..23]

-RD

-WR

-CS1

V3.3

GND

-RESET

IRDA_TXD

IRDA_RXD

IRDA_SD

D[0..7]

A[0..23]

A[0..23]

-CSFLASH

-RESFLASH

-FLASHWE

-WR

-WR

-RD

-RD

D[0..7]

-CS1

-IOREQ

-MREQ

-INSTRD

-WAIT

-HALT_SLP

-BUSREQ

-BUSACK

-NMI

CLK_OUT

RTC_VDD

IICSDA

IICSCL

PB[0..7]

PC[0..7]

JTAG[1..4]

D[0..7]

A[0..23]

-CS[0..3]

JTAG[1..4]

-FLASHWE

RTC_VDD

-RESET

CLK_OUT

-RD

-WR

-NMI

-BUSACK

-BUSREQ

-IOREQ

-MREQ

-INSTRD

-WAIT

-HALT_SLP

IICSCL

IICSDA

PB[0..7]

PC[0..7]

PD[0..7]

ETHIRQ

-SLEEP

-ACTIVE

-CSFLASH

-WR

-RESET

-ETHWR

-ACT

IVE

SA[0..3]

PD[0..7]

-RESFLASH

IRDA_TXD

IRDA_SD

D[0..7]

-ETHRD

-DIS_IRDA

-CS[0..3]

IRDA_RXD

SD[0..7]

ETHIRQ

A[0..23]

-RD

-SLEE

P

V3.3

GND

TDO

TDO

-DIS_FL

IOCHRDY

-WAIT