Zilog EZ80L92 User Manual

Page 55

eZ80L92 Development Kit

User Manual

UM012913-0407

Operational

Description

51

The eZ80L92 Module features an Infrared Encoder/Decoder register that

configures the IrDA function. This register is located at address

0BFh

in

the internal I/O register map.

The Infrared Encoder/Decoder register contains three control bits. Bit 0

enables or disables the IrDA encoder/decoder block. Bit 1, if set, enables

received data to pass into the UART0 Receive FIFO data buffer. Bit 2 is a

test function that provides a loopback sequence from the TxD pin to the

RxD input.

Bit 1, the Receive Enable bit, is used to block data from filling up the

Receive FIFO when the eZ80L92 Module is transmitting data. Because

IrDA data passes through the air as a light source, transmitted data can

also be received. This Receive Enable bit prevents the data from being

received. After the eZ80L92 Module completes transmitting, this bit is

changed to allow for incoming messages.

The code below provides an example of how this function is enabled on

the eZ80L92 Module.

//Init_IRDA

// Make sure to first set PD2 as a port bit, an output and set it Low.

PD_ALT1 &= 0xFC;

// PD0 = uart0tx, PD1 = uart0_rx

PD_ALT2 |= 0x03;

// Enable alternate function

UART_LCTL0= 0x80;

// Select dlab to access baud rate generator

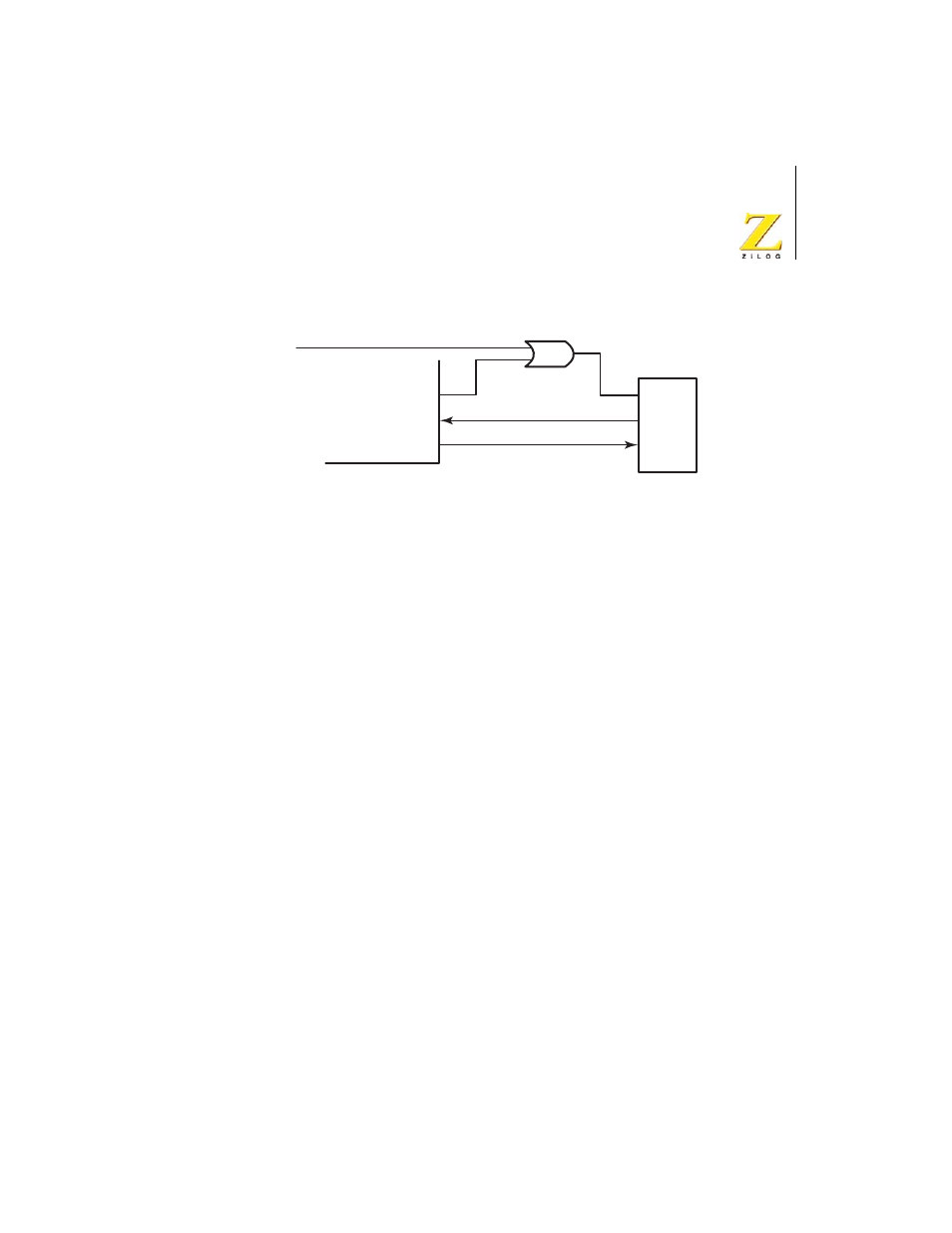

Figure 14. IrDA Hardware Connections

External Disable

eZ80L92

Device

IrDA

PD2(IR_SD)

PD1(RxD)

PD0(TxD)

SD

RD

TD