Schematic diagrams, Ez80acclaim® development platform, Ez80acclaim – Zilog EZ80L92 User Manual

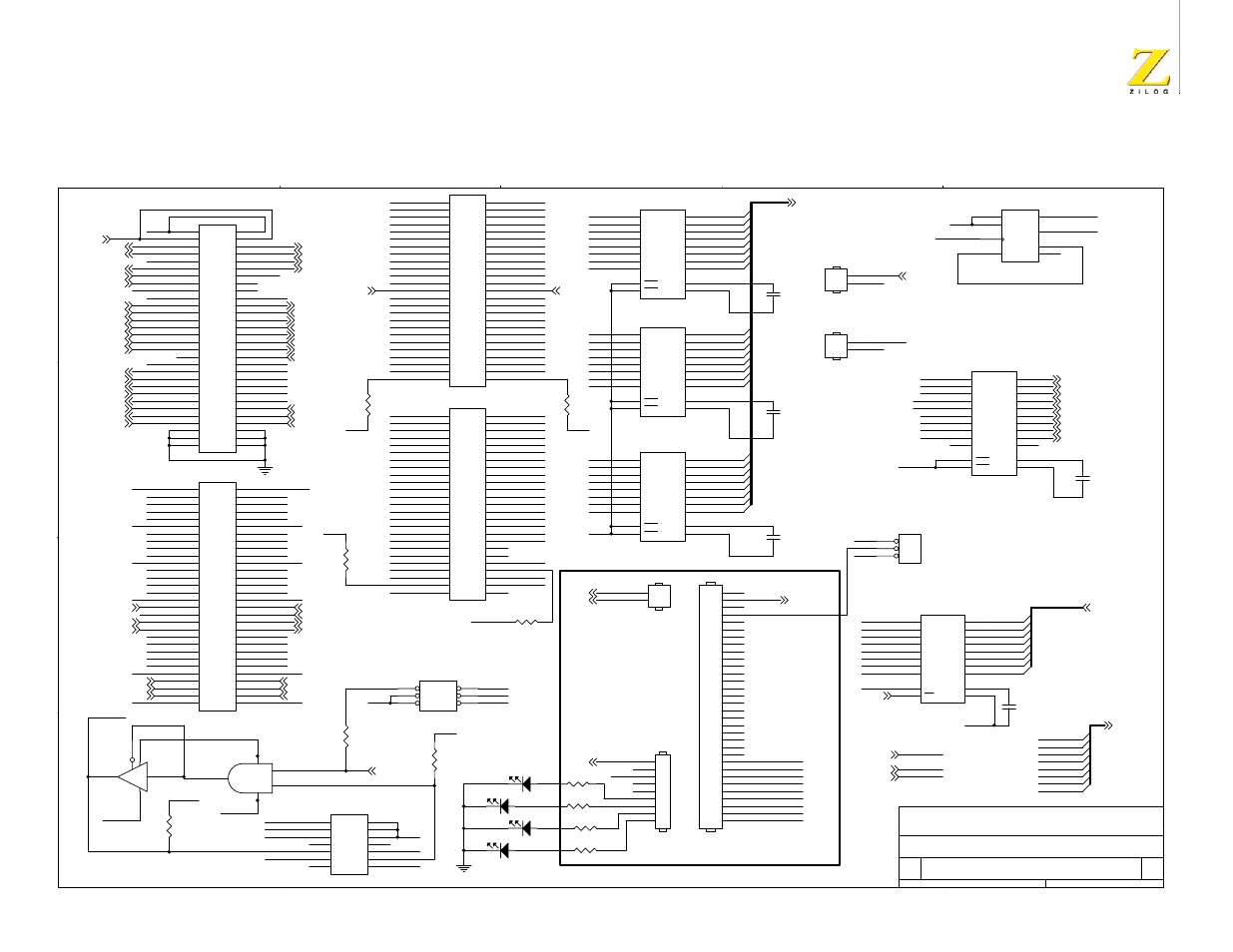

Page 65: D in the, Development platform, Figure 17. ez80acclaim, Development platform schematic diagram, #1 of 5

UM012913-0407

Schematic

Diagrams

eZ80L92 Development Kit

User Manual

61

Schematic Diagrams

eZ80Acclaim

®

Development Platform

through

diagram the layout of the eZ80Acclaim!

®

Development Platform.

Figure 17. eZ80Acclaim!

®

Development Platform Schematic Diagram, #1 of 5

5

4

3

2

1

D

C

B

A

DO NOT USE J6_17 AND J6_35

MODEM CONNECTORS

MODEM's

AGND

ZDI

INTERFACE

DCD

RX

DTR

TX

Connectors

96C0858-001

C

Schematic, eZ80L92 Evaluation Board

ZiLOG

910 E. Hamilton Avenue

B

1

4

Friday, October 10, 2003

Title

Size

Document Number

Rev

Date:

Sheet

of

TCK

TDI

TDO

TDI

TRIGOUT

TCK

TMS

PRSTn

VDD

PB2_SS

D3

VDD

PB6_MISO

D2

D4

VDD

A20

GND

A6

A14

D5

GND

D6

A9

GND

PB1_T1_I

GND

GND

GND

D0

A0

A23

A11

GND

GND

A5

GND

PB7_MOSI

PB0_T0_I

A4

A19

A2

A16

A21

A12

-RESET

VDD

D1

GND

A1

A17

A7

GND

GND

GND

A8

D7

PHI

VDD

GND

A22

A13

A3

A18

PB3_SCK

GND

GND

A10

A15

VDD

VDD

VDD

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

A0

A1

A2

A3

A4

A5

A6

A7

A11

MA15

MA11

A14

MA12

A13

A15

A9

MA8

MA9

A12

MA13

A10

MA14

MA10

A8

A16

A22

A19

MA21

MA19

MA17

MA20

A23

A21

MA23

MA18

A18

MA16

A17

MA22

A20

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

D1

D2

D0

D4

D3

D5

D6

D7

-M_RD

D[7:0]

A[23:0]

SCL

SDA

VDD

ID_0

ID_1

ID_2

9V_DC

GND

PC6_DCD1

PC2_RTS1

-MRESET

PC1_RXD1

PC3_CTS1

PC5_DSR1

PC0_TXD1

PC7_RI1

GND

PC4_DTR1

MA6

MA10

GND

MA8

MA13

MA15

MA18

MA19

MA2

MA11

MA4

MA5

-DIS_ETH

MA21

MA22

-M_CS0

-M_CS2

MD1

MD3

MD5

MD7

-M_MEMRQ

GND

-M_WR

-BUSACK

MD6

MA16

VDD

MD2

MA9

-M_RD

GND

VDD

MA0

MA12

MA17

MA1

INSTRD

MA23

MD0

MD4

MA7

-DIS_FL

-M_IORQ

MA3

GND

MA20

-M_CS1

MA14

-M_CS3

PC4_DTR1

PB3_SCK

VDD

SCL

GND

VDD

-FLASHWE

TDO

PB7_MOSI

PD6_DCD0

PD3_CTS0

PC0_TXD1

HALT_SLP

GND

RTC_VDD

SDA

PB1_T1_I

PD1_RXD0

-RST

PB5_T5_O

PC2_RTS1

PD5_DSR0

TCK

-DIS_IRDA

PC3_CTS1

PB2_SS

GND

PC7_RI1

GND

TDI

PB6_MISO

GND

PD2_RTS0

PD7_RI0

-NMI

TRIGOUT

M_PHI

PB0_T0_I

PD0_TXD0

PB4_T4_O

PC1_RXD1

PD4_DTR0

TMS

PC5_DSR1

GND

VDD

-M_CS0

-M_CS1

-M_CS2

M_TIP

M_RING

GND

GND

GND

VCC

GND

GND

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

PC6_DCD1

VDD

VDD

-BUSREQ

VDD

GND

VDD

VCC

GND

VDD

-MWAIT

PB4_T4_O

PB5_T5_O

-CS3

-FLASHWE

GND

GND

GND

VDD

GND

GND

GND

GND

VDD

GND

VDD

VDD

VCC

VCC

VDD

TVCC_RESETn

VDD

GND

-M_IORQ

-M_MEMRQ

-M_WR

-M_RD

-M_CS3

M_PHI

PRSTn

-RST

PC3_CTS1

-MOD_DIS

PD0_TXD0

-NMI

PC4_DTR1

PD1_RXD0

-CS0

INSTRD

PD2_RTS0

PHI

PD7_RI0

-CS2

-RD

PD4_DTR0

-BUSREQ

PC1_RXD1

PD5_DSR0

PD3_CTS0

PC2_RTS1

-CS1

PC5_DSR1

-IORQ

PC7_RI1

PC6_DCD1

PC0_TXD1

-CON_DIS

-WR

PD6_DCD0

-MEMRQ

-BUSACK

-RESET

EM_D1

EM_D2

EM_D3

EM_D4

EM_D5

EM_D6

EM_D7

D[7:0]

A[23:0]

EM_D0

-MWAIT

-MRESET

-MOD_DIS

-CS0

-CS1

-CS2

-CS_EX

SCL

SDA

MD[7:0]

VDD

GND

VCC

9VDC

PB2_SS

PB1_T1_I

PB0_T0_I

-DIS_FL

ID_0

ID_1

ID_2

M_TIP

M_RING

-L_RD

-DIS_ETH

-DIS_IRDA

-IORQ

-MEMRQ

PHI

-WR

-RD

-CS3

J1

HEADER 32

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

R1

10K

JP2

Header 25x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

D1

2

1

C34

0.1uF

R9

0

J2

HEADER 2

1

2

D2

2

1

C31

0.1uF

D4

2

1

P1

con 7x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

R8

0

R2

10K

U1

74LVC244A

2

4

6

8

1

18

16

14

12

20

10

11

13

15

17

9

7

5

3

19

A1

A2

A3

A4

1OE

Y1

Y2

Y3

Y4

VCC

GND

A5

A6

A7

A8

Y5

Y6

Y7

Y8

2OE

C1

0.1uF

J4

Header 3x2

1

2

3

4

5

6

J5

HEADER 2

1

2

J8

Header 30x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

R3

10K

R19

10K

R5

1K

C33

0.1uF

U8A

TC74LVT125

2

3

14

1

7

U21

74LVC827/SO

12

24

23

22

21

20

19

18

17

16

2

3

4

5

6

7

8

9

13

1

10

11

15

14

GND

VCC

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

A1

A2

A3

A4

A5

A6

A7

A8

OE2

OE1

A9

A10

Y9

Y10

J12

Header 3

1

2

3

R24

10K

U5

74LVC244A

2

4

6

8

1

18

16

14

12

20

10

11

13

15

17

9

7

5

3

19

A1

A2

A3

A4

1OE

Y1

Y2

Y3

Y4

VCC

GND

A5

A6

A7

A8

Y5

Y6

Y7

Y8

2OE

R4

10K

R20

0

J7

HEADER 2

1

2

U2

AT24C128

1

2

4

5

6

7

8

3

A0

A1

GND

SDA

SCL

WP

VCC

NC

U3

74LVC244A

2

4

6

8

1

18

16

14

12

20

10

11

13

15

17

9

7

5

3

19

A1

A2

A3

A4

1OE

Y1

Y2

Y3

Y4

VCC

GND

A5

A6

A7

A8

Y5

Y6

Y7

Y8

2OE

D3

2

1

U9A

TC74LVC08

1

2

3

14

7

J9

HEADER 9

1

2

3

4

5

6

7

8

9

R21

0

U7

74LVC245/SO

2

3

4

5

6

7

8

9

19

1

18

17

16

15

14

13

12

11

20

10

A0

A1

A2

A3

A4

A5

A6

A7

OE

DIR

B0

B1

B2

B3

B4

B5

B6

B7

VCC

GND

JP1

Header 25x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

J6

Header 30x2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

C30

0.1uF