Altera Partial Reconfiguration IP Core User Manual

Page 7

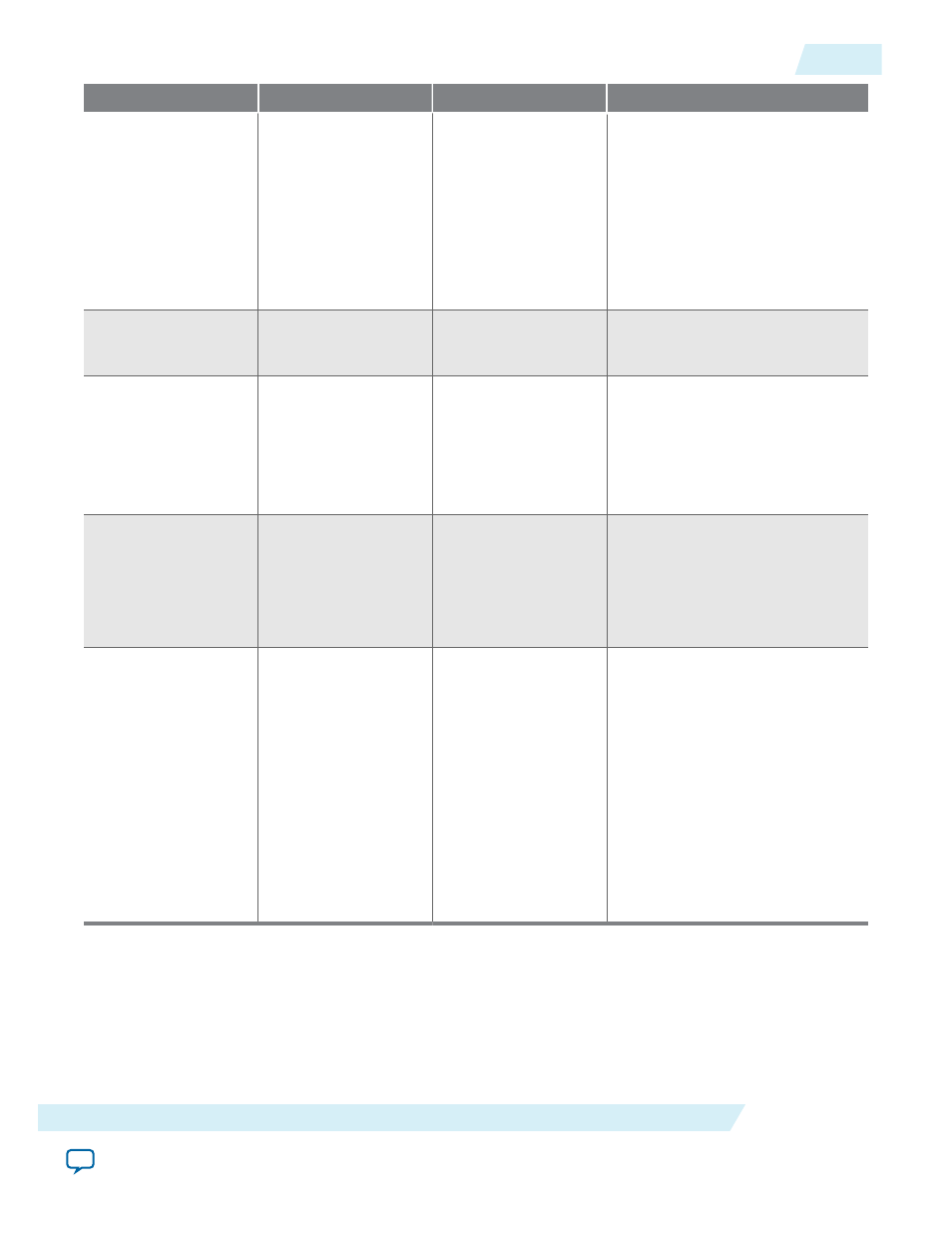

IP Core Option

Value

Default

Description

PR bitstream ID

-2147483648 to

2147483647

0

Specifies a signed 32-bit integer

value of the PR bitstream ID for

External Host. This value must

match the PR bitstream ID

generated during compilation

for the target PR design. The PR

bitstream ID value of the target

PR design can be found in the

Assembler compilation report

(.asm.rpt).

Input Data Width

1, 2, 4, 8, 16, or 32

16

Specifies the data width in bits.

This option affects the

data[]

bus width.

Target device

familiy for partial

reconfiguration

"Arria V", "Arria V

GZ", "Cyclone V",

"Stratix V"

"Stratix V"

Select the target device family for

partial reconfiguration when the

PR megafunction is used as

External Host.

Note: This option is ignored

for PR Internal Host.

Clock-to-Data ratio 1, 2, or 4

1

Specifies the ratio between PR

clock and PR data. Select '1' for

plain PR data, '2' for encrypted

PR data, or '4' for compressed PR

data (with or without

encryption)

Divide error

detection frequency

by

1, 2, 4, 8, 16, 32, 64,

128, or 256

1

Only available when the IP core

is used as an Internal Host where

the

crcblock

WYSIWYG atom

primitive is auto-instantiated as

part of the design.

Specifies the divide value of the

internal clock, which determines

the frequency of the error

detection CRC. The divide value

must be a power of two. Refer to

the device handbook to find the

frequency of the internal clock

for the selected device.

Related Information

•

Using the Avalon Memory Mapped Slave Interface

•

Avalon Memory Map Slave Interface Read and Write Transfer Timing

on page 17

For more information on the timing specification for the Avalon Memory Mapped Slave interface.

UG-PARTRECON

2015.05.04

Partial Reconfiguration IP Core Parameters

7

Partial Reconfiguration IP Core

Altera Corporation