Altera Partial Reconfiguration IP Core User Manual

Partial reconfiguration ip core

Partial Reconfiguration IP Core

2015.05.04

UG-PARTRECON

Partial reconfiguration (PR) is fully supported in the Stratix

®

V device family, which offers you the ability

to reconfigure part of the design's core logic such as LABs, MLABs, DSP, and RAM, while the remainder

of the design continues running. The PR IP core can be implemented through the Qsys Interface, or via

the Quartus II

®

IP Catalog.

Partial reconfiguration is performed through either an internal host residing in the core logic or as an

external host via dedicated PR pins. The advantage of the internal host is that you can store all the logic

needed for PR on the device, without the need for external devices.

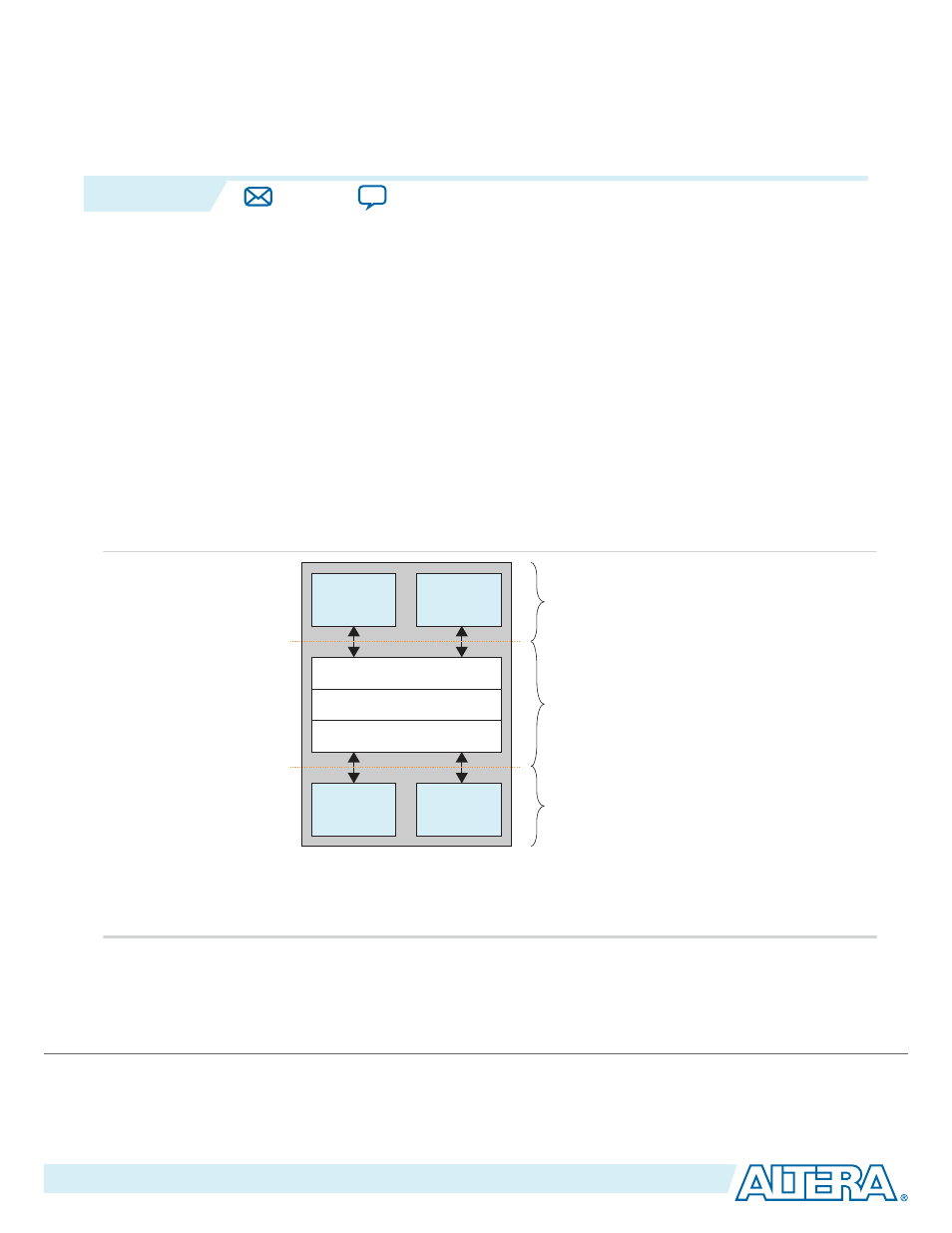

Figure 1: PR IP core Components

When you instantiate the PR IP core, the Main Controller module which includes the Control Block

Interface Controller, Freeze/Unfreeze Controller, and the Data Source Controller are all instantiated. A

Data Source Interface module provides you with a JTAG Debug Interface and PR Data Interface. If you

choose to use the PR IP core as an internal host, it automatically instantiates the corresponding

crcblock

and

prblock

WYSIWYG atom primitives.

CRCBLOCK

PRBLOCK

CB Interface Controller

Freeze/Unfreeze Controller

Data Source Controller

JTAG Debug

Interface

PR Data

Interface

FPGA Control

Block (CB)

Interface Module

Main Controller

Module

(1)

PR Data Source

Interface Module

Note:

1. The main controller module handles all the handshaking signals of the

CB interface and processes the incoming data, as needed, before sending

to the PRBLOCK. It also handles the freeze/un-freeze PR interface.

If it is used as external host (placed in another FPGA or CPLD), the PR IP core provides the

crcblock

and

prblock

WYSIWYG atom primitive as interface ports so that you can connect to the dedicated PR

pins and

CRC_ERROR

pin on the target FPGA undergoing partial reconfiguration.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Document Outline

- Partial Reconfiguration IP Core

- Instantiating the Partial Reconfiguration IP Core in the Qsys Interface

- Instantiating the Partial Reconfiguration IP Core in the Quartus II IP Catalog

- Bitstream Compatibility Check

- Partial Reconfiguration IP Core Parameters

- Partial Reconfiguration IP Core Ports

- Using the Avalon Memory Mapped Slave Interface

- Avalon Memory Map Slave Interface Data/CSR Memory Map

- FPGA Control Block Interface

- Control Block Interface Controller

- Freeze and Unfreeze Controls

- Data Source Controller

- Standard Partial Reconfiguration Data Interface

- JTAG Debug Mode for Partial Reconfiguration

- Sample Freeze Wrapper for Multiple PR Regions

- Sample PR IP Core as an External Host on the Same Device

- Revision History