Altera Partial Reconfiguration IP Core User Manual

Page 12

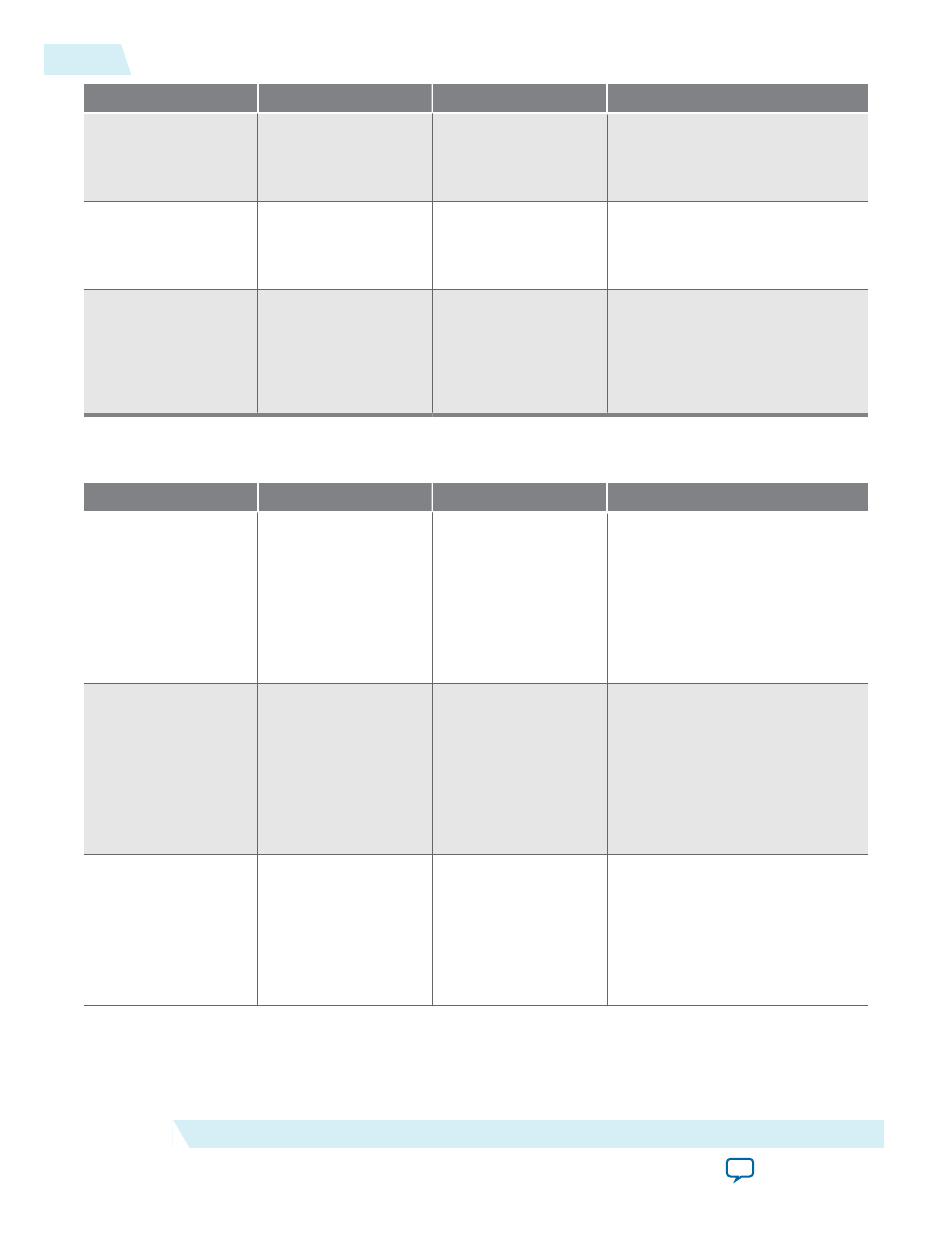

Port Name

Width

Direction

Function

avmm_slave_write

1

Input

Avalon-MM write control.

This signal is ignored during

JTAG debug operations.

avmm_slave_

writedata

16 or 32

Input

Avalon-MM write data bus.

This signal is ignored during

JTAG debug operations.

avmm_slave_

waitrequest

1

Output

Asserted to indicate that the IP is

busy and it is unable to respond

to a read or write request.

This signal is pulled high during

JTAG debug operations.

Table 5: External Host Interface

These options are available when Use as PR Internal Host parameter is turned Off.

Port Name

Width

Direction

Function

crc_error_pin

1

Input

Available when you use the PR

IP core as an External Host.

Connect this port to the

dedicated

CRC_ERROR

pin of the

FPGA undergoing partial

reconfiguration, or connect

directly to the

crcblock

WYSIWYG atom primitive.

pr_ready_pin

1

Input

Available when you use the IP

core as an External Host.

Connect this port to the

dedicated

PR_READY

pin of the

FPGA undergoing partial

reconfiguration, or connect

directly to the

prblock

WYSIWYG atom primitive.

pr_error_pin

1

Input

Available when the IP is used as

the External Host. Connect this

port to the dedicated

PR_ERROR

pin of the FPGA undergoing

partial reconfiguration, or

connect directly to the

prblock

WYSIWYG atom primitive.

12

Partial Reconfiguration IP Core Ports

UG-PARTRECON

2015.05.04

Altera Corporation

Partial Reconfiguration IP Core