Altera Partial Reconfiguration IP Core User Manual

Page 16

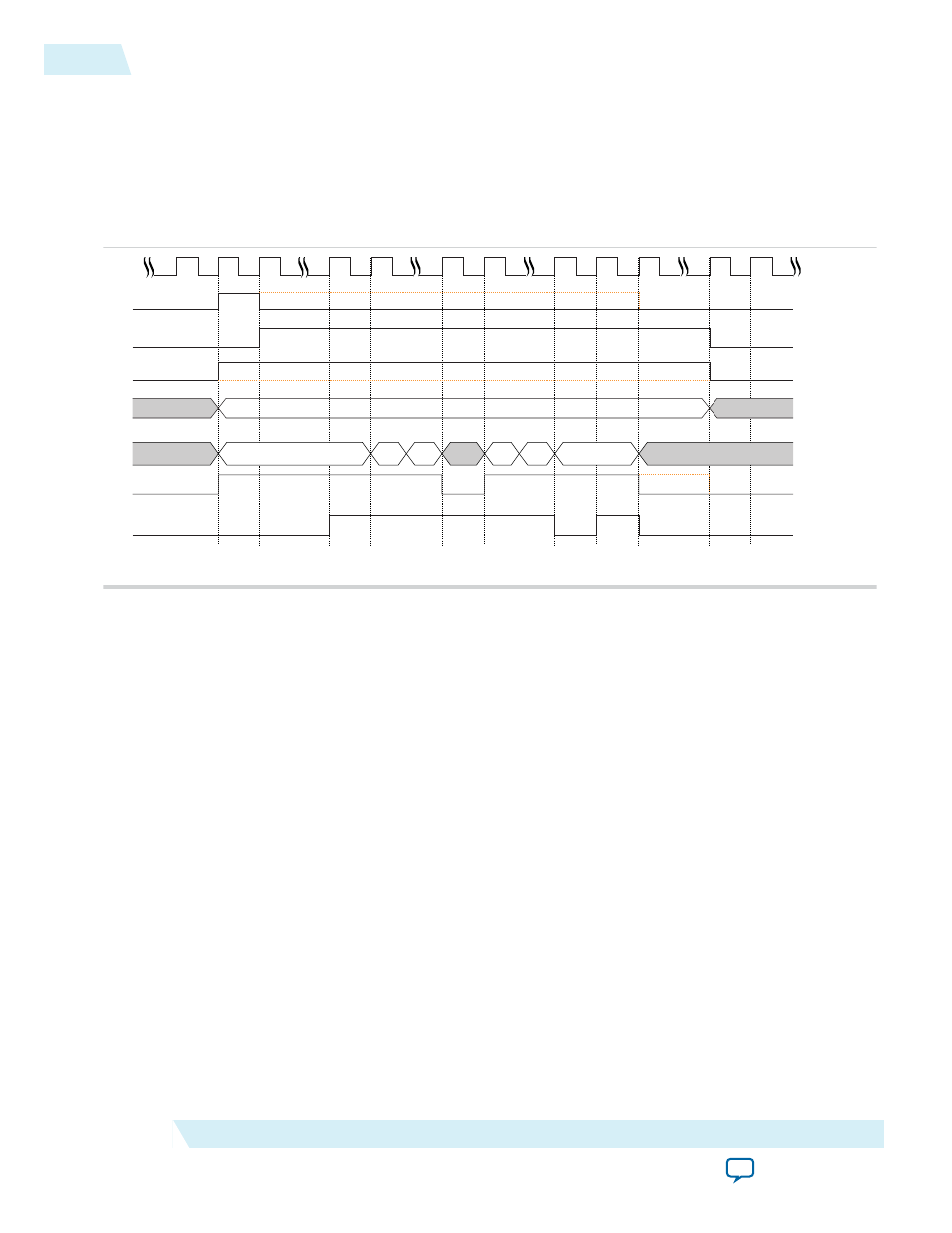

Partial Reconfiguration IP Core Timing Specification

This timing diagram illustrates a successful Partial Reconfiguration IP core operation. Pass or fail can be

determined with the

status[2:0]

output signal.

The PR operation is initated when you assert the

pr_start

signal. You can monitor the

status[]

or

freeze

signals to detect the end of the PR operation.

Figure 5: Partial Reconfiguration Timing

clk

pr_start

freeze

double_pr

status[2:0]

data[]

data_valid

data_ready

D1 (First Data)

D2

D3

D6 (Last Data)

Dummy Data

D4

D5

(1)

(2)

(3)

(4)

(5)

(6)

(7)

Note:

1. You must assert

pr_start

signal high for a minimum of one clock cycle to initiate PR and deassert

pr_start

before sending the last data.

2.

status[]

signal is reset when

pr_start

is asserted and changes during a PR operation if any error

such as a

CRC_ERROR

,

PR_ERROR

, or bitstream incompatibility error is detected.

3.

status[]

signal changes after a PR operation if

CRC_ERROR

is detected and no error happens during

the previous PR operation.

4. The

data_valid

signal is not required to be asserted at the same time as the

pr_start

. You can

provied the

data[]

and assert

data_valid

when appropriate.

5. You can either drive the

data_valid

signal low after sending the last data, or contiue to assert

data_valid

high with dummy data on

data[]

until the end of PR, when

freeze

is driven low or

status[]

is updated/

6.

data[]

is transferred only when

data_valid

and

data_ready

are asserted on the same cycle. Do not

drive new data on the data bus, when both

data_valid

and

data_ready

have not been asserted high.

7. The

data_ready

signal is driven low once the PR IP Core receives the last data.

The

data[]

,

data_valid

, and

data_ready

signals comply with the Avalon-ST specification for Data

Transfer with Backpressure. The PR IP Core acts as a sink, with

readLatency = 0

. For more information,

refer to the Avalon Interface Specifications.

If your

CDRATIO

is not 1, or your

data[]

width is x32 for series-V devices, the

data_ready

alternates

between high and low for one or more clock cycles. The PR IP Core requires additional clock cycles to

process the data recieved. You should hold

data[]

when

data_ready

is low.

Important: The

PR_CLK

signal has a different nominal maximum frequency for each device. Most Stratix

V devices have a nominal maximum frequency of at least 62.5 MHz.

16

Partial Reconfiguration IP Core Timing Specification

UG-PARTRECON

2015.05.04

Altera Corporation

Partial Reconfiguration IP Core