Freeze and unfreeze controls, Data source controller, Standard partial reconfiguration data interface – Altera Partial Reconfiguration IP Core User Manual

Page 18

The controller receives data and sends it to the

prblock

WYSIWYG atom primitive during a PR event

with the clock-to-data ratio (CDRATIO) you specify when you instantiate the Partial Reconfiguration IP

core.

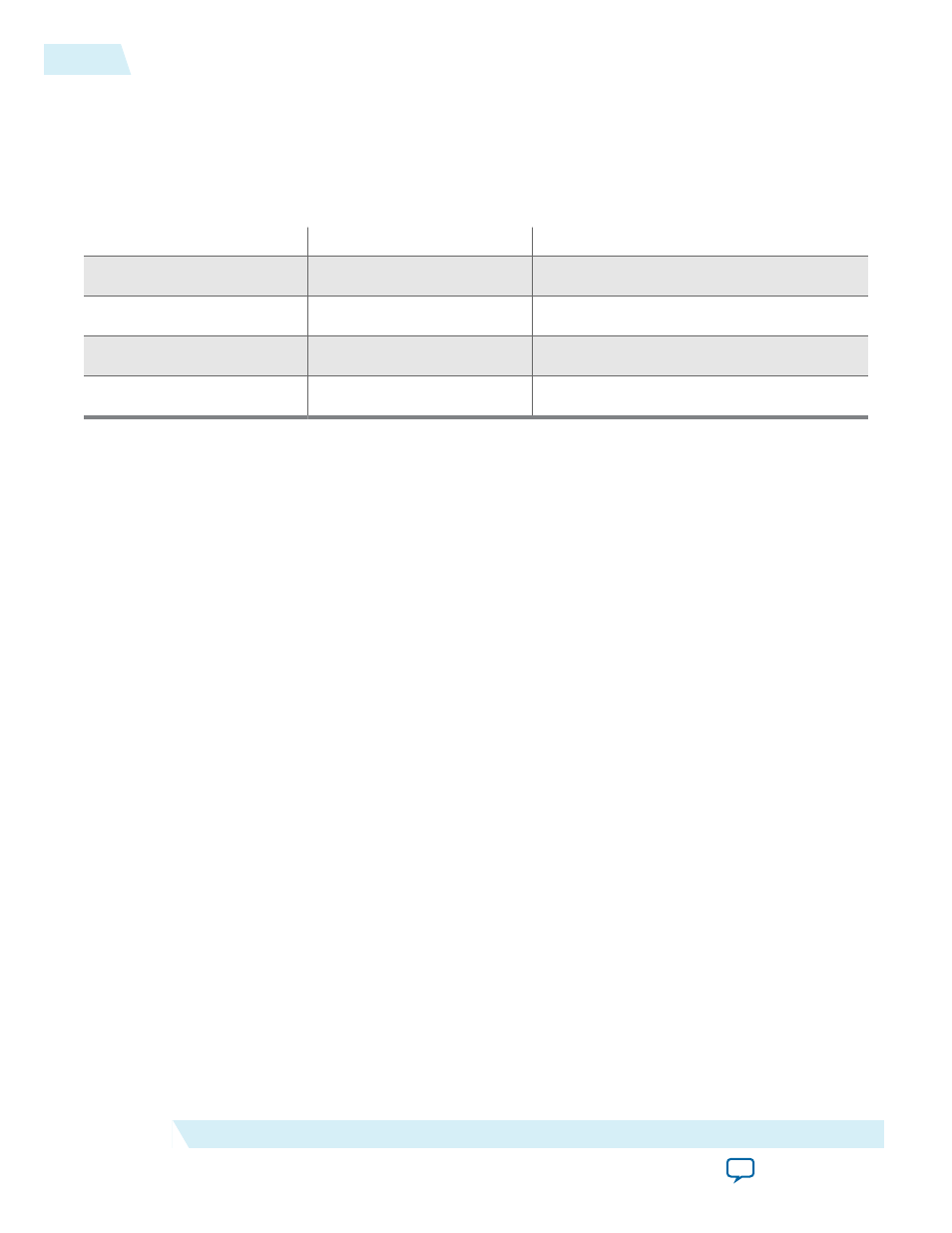

Table 8: CDRATIO for PR Compression and/or Encryption

The following table lists the range of values for the clock-to-data ratio for bitstreams that are compressed,

encrypted, both, or neither.

Compressed

Encrypted

Clock-to-Data Ratio

No

No

x1

No

Yes

x2

Yes

No

x4

Yes

Yes

x4

Related Information

Instantiating the Partial Reconfiguration IP Core in the Quartus II IP Catalog

Freeze and Unfreeze Controls

The Freeze/Unfreeze controller logic of the Partial Reconfiguration IP core provides a signal to the user

specified PR regions, freezing all input signals during PR operation to avoid current contention.

You begin a PR event by asserting the

pr_start

input port to the PR IP core. The Freeze/Unfreeeze

Controller then asserts the output freeze signal high and sends it to the PR region you specified. All the

input signals coming into that PR region are then pulled high, preventing current contention in the

device. The PR IP core does not differentiate between multiple PR regions, so you may need to create

custom freeze logic if you are freezing individual PR regions.

Once the PR operation is completed, this controller asserts the output freeze signal low. All the input

signals coming into the specified PR region are released and the PR region is ready for normal operation.

Related Information

•

Partial Reconfiguration IP Core Timing Specification

•

Partial Reconfiguration IP Core Ports

on page 8

Data Source Controller

This controller handles the source of PR data, either from JTAG or standard data interface.

The JTAG interface takes precedence over the standard PR data interface. For example, whenever JTAG is

engaged through command from Quartus II Programmer tool, the PR data is sourced from the JTAG

interface rather than the PR data interface.

Standard Partial Reconfiguration Data Interface

18

Freeze and Unfreeze Controls

UG-PARTRECON

2015.05.04

Altera Corporation

Partial Reconfiguration IP Core