Fpga control block interface – Altera Partial Reconfiguration IP Core User Manual

Page 15

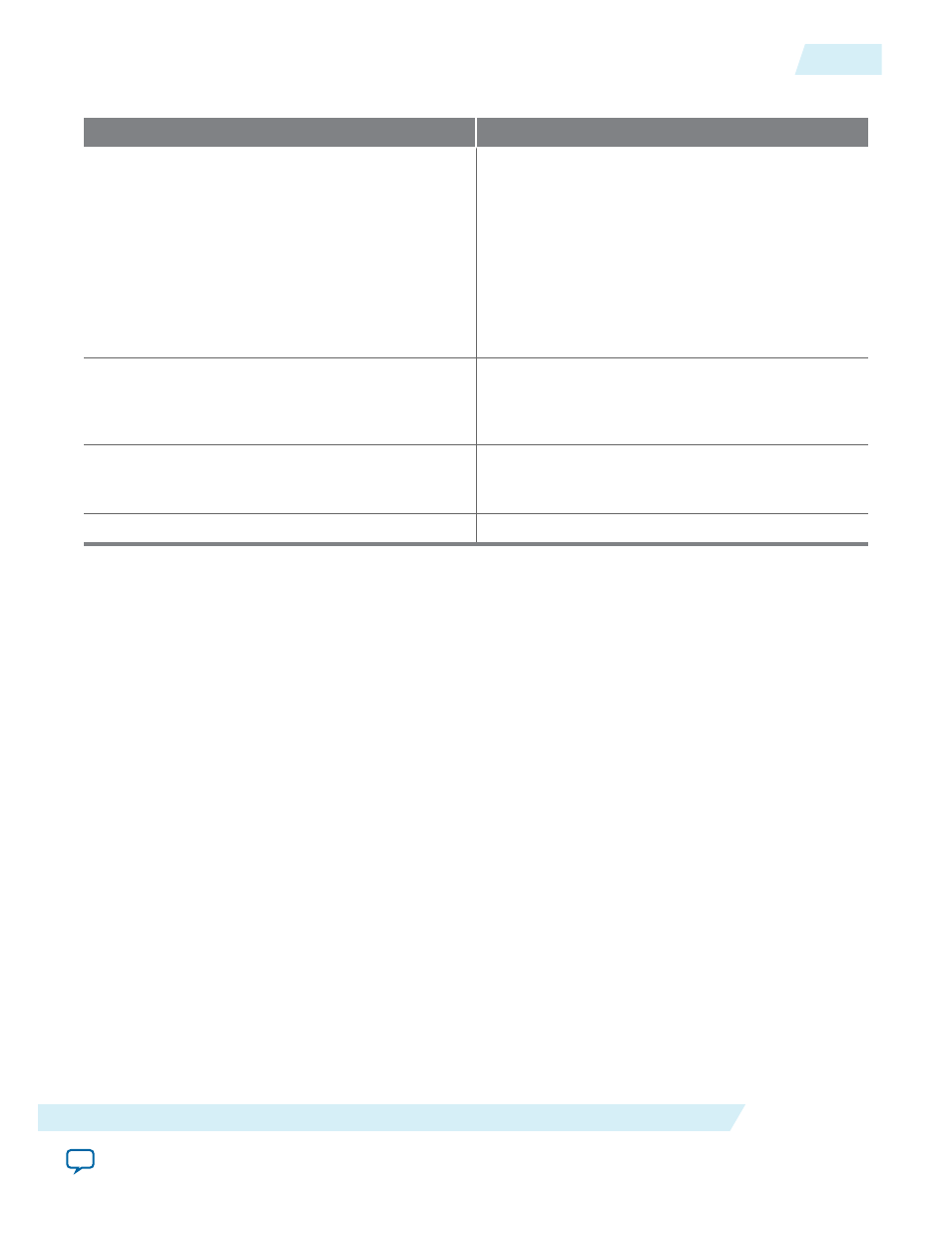

Table 7: PR_CSR Control and Status Registers

Bit Offset

Description

0

Read and write control register for pr_start signal.

Refer to “Input/output Port List” section for more

details on pr_start signal.

pr_start = PR_CSR[0]

PR_CSR[0]

is de-asserted to value “0” by the IP core

automatically one clock cycle after it is asserted to

streamline the flow so you do not need to manually

assert and de-assert this register to control

pr_

start

signal.

1

Read and write control register for

double_pr

signal.

double_pr = PR_CSR[1]

2-4

Read only status register for

status[2:0]

signal.

PR_CSR[4:2] = status[2:0]

5-15 or 5-31

(1)

Reserved

Related Information

•

Avalon Memory Map Slave Interface Read and Write Transfer Timing

on page 17

•

Partial Reconfiguration IP Core Ports

on page 8

FPGA Control Block Interface

When you instantiate the PR IP core, you can choose to use it as either an internal host or external host.

If it is used as an internal host, the PR IP core auto instantiates the corresponding device

crcblock

and

prblock

WYSIWYG atom primitive. If PR is used as external host (placed in another FPGA or CPLD),

the PR IP core provides the

crcblock

and

prblock

interface ports so you can connect the host to the

dedicated PR pins and CRC_ERROR pin on the target FPGA being partially reconfigured.

Note: You may need to instantiate the PR IP core as an external host to share the

crcblock

and

prblock

interface even though the PR IP core is located inside the FPGA being partially reconfigured. For

example; your design uses another piece of IP, which instantiates its own

crcblock

WYSIWYG

atom primitive to unload the Error Message Register (EMR) whenever

CRC_ERROR

is detected. Your

design must share the

crcblock

interface signals between the PR IP core and secondary IP,

otherwise the Quartus II compilation will fail because more than one

crcblock

is not allowed.

You can also instantiate the PR IP core as the external host so be able to add

crcblock

and

problock

WYSIWYG atom primitive instances to SignalTap II for debugging purposes.

UG-PARTRECON

2015.05.04

FPGA Control Block Interface

15

Partial Reconfiguration IP Core

Altera Corporation