Altera Partial Reconfiguration IP Core User Manual

Page 11

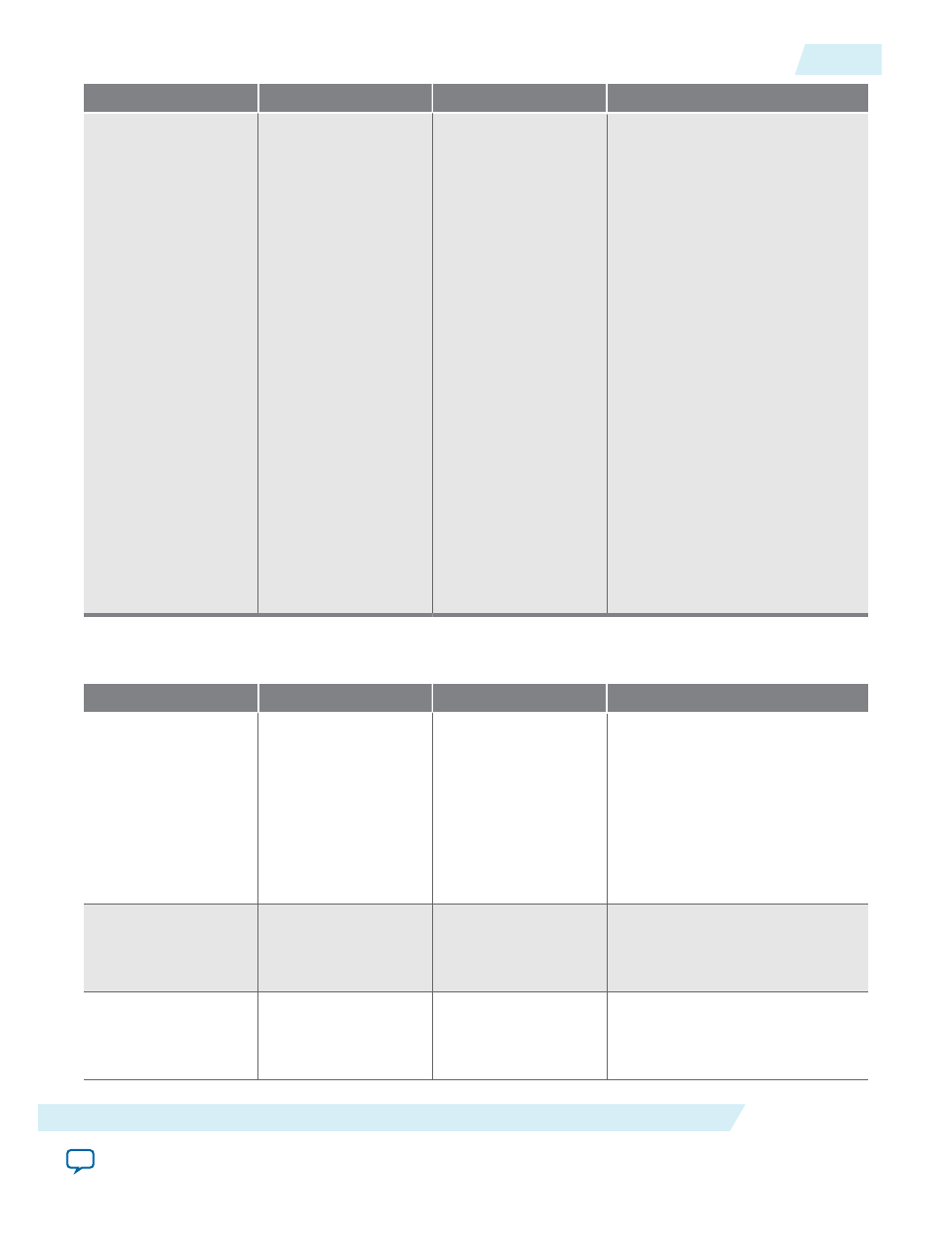

Port Name

Width

Direction

Function

double_pr

1

Input

When the

pr_start

signal is

triggered until the de-assertion

of

freeze

signal, a signal

asserted high on this port

indicates the PR event requires

double PR cycle. A low signal on

this port indicates a single PR

cycle event.

If your design requires the use of

double PR because you have

initialized RAM in the PR

region, you must assert the

double_pr

input signal high so

that the controller can handle

double PR properly.

You must assert this signal high

if the PR bitstream (

.rbf

) is

generated with the Write

memory contents option turned

on. Failure to do so causes a

PR_

ERROR

assertion during partial

reconfiguration.

This signal is ignored during

JTAG debug operations.

Table 4: Avalon-MM Slave Interface

These options are available when Enable Avalon-MM Slave Interface parameter is turned On.

Port Name

Width

Direction

Function

avmm_slave_

address

1

Input

Avalon-MM address bus. The

address bus is in the unit of

Word addressing.

Refer to the Qsys Component

section for more details on the

address mapping.

This signal is ignored during

JTAG debug operations.

avmm_slave_read

1

Input

Avalon-MM read control.

This signal is ignored during

JTAG debug operations.

avmm_slave_

readdata

16 or 32

Output

Avalon-MM read data bus.

This signal is ignored during

JTAG debug operations.

UG-PARTRECON

2015.05.04

Partial Reconfiguration IP Core Ports

11

Partial Reconfiguration IP Core

Altera Corporation