Control block interface controller – Altera Partial Reconfiguration IP Core User Manual

Page 17

Related Information

Avalon Interface Specifications for data transfer with backpressure

Avalon Memory Map Slave Interface Read and Write Transfer Timing

The Avalon-MM interface supports read and write transfers with a slave-controlled

waitrequest

. The

slave can stall the interconnect for as many cycles as required by asserting the

waitrequest

signal. If a

slave uses

waitrequest

for either read or write transfers, it must use

waitrequest

for both.

A slave typically receives

address

,

read

or

write

, and

writedata

after the rising edge of the clock. A

slave asserts

waitrequest

before the rising clock edge to hold off transfers. When the slave asserts

waitrequest

, the transfer is delayed. And, the address and control signals are held constant. Transfers

complete on the rising edge of the first

clk

after the slave port deasserts

waitrequest

.

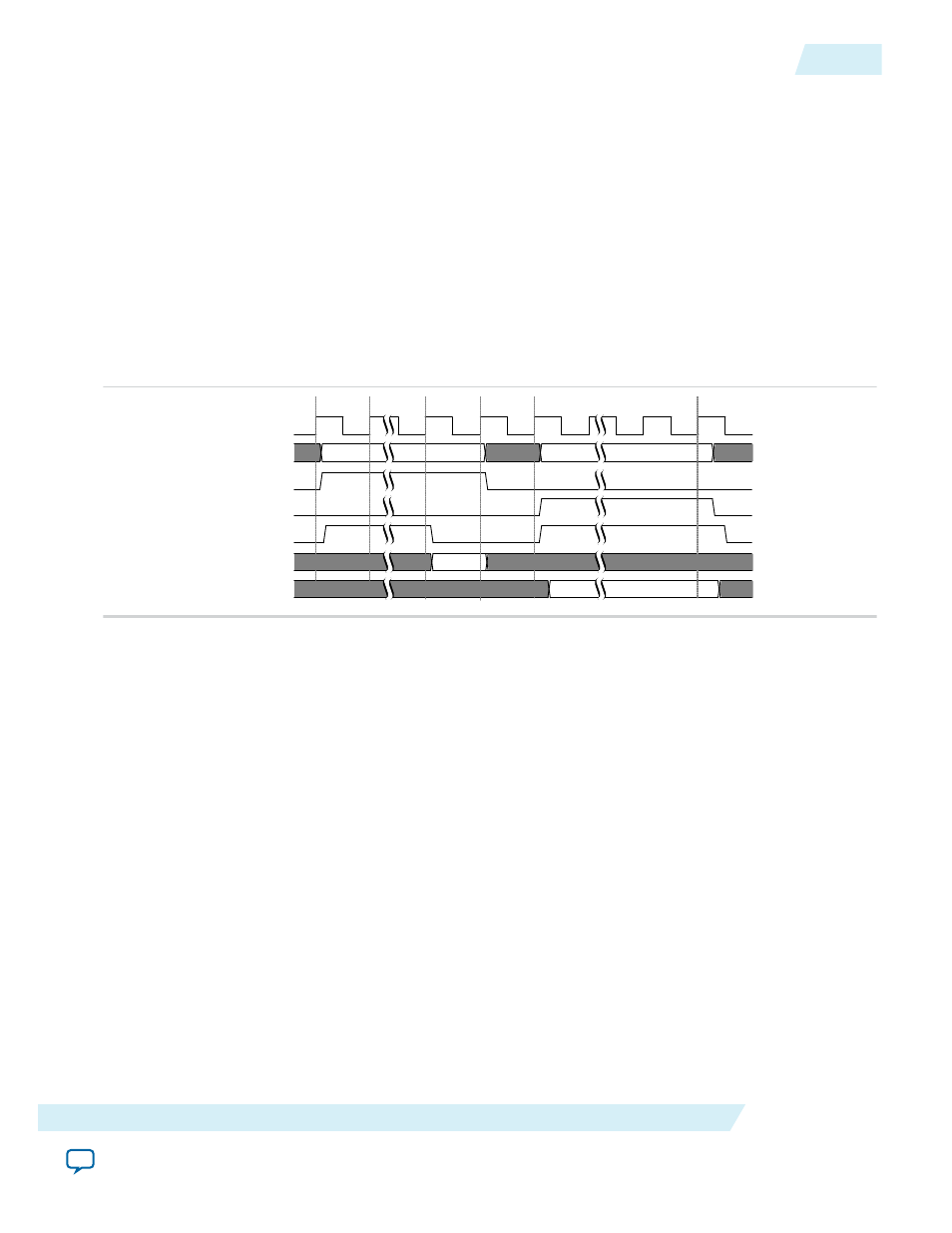

Figure 6: Read and Write Transfers for Avalon-MM Slave Interface

clk

address

read

write

waitrequest

readdata

writedata

address

readdata

writedata

1

2

3

4

5

6

The numbers in this timing diagram, mark the following transitions:

1.

address

and

read

are asserted after the rising edge of

clk

.

waitrequest

is asserted stalling the

transfer.

2.

waitrequest

is sampled. Because

waitrequest

is asserted, the cycle becomes a wait-state.

address

,

read

, and

write

remain constant.

3. The slave presents valid

readdata

and deasserts

waitrequest

.

4.

readdata

and deasserted

waitrequest

are sampled, completing the transfer.

5.

address

,

writedata

, and

write

signals are asserted. The slave responds by asserting

waitrequest

stalling the transfer.

6. The slave captures

writedata

and deasserts

waitrequest

ending the transfer.

Related Information

For more information on read and write transfers with Avalon Memory Mapped Interfaces

Control Block Interface Controller

This controller handles all the handshaking signals of the

prblock

WYSIWYG atom primitive and it will

monitor

CRC_ERROR

signals of

crcblock

WYSIWYG atom primitives throughout the PR event (before,

during, and after PR) to detect any CRAM error.

UG-PARTRECON

2015.05.04

Avalon Memory Map Slave Interface Read and Write Transfer Timing

17

Partial Reconfiguration IP Core

Altera Corporation