The power monitor, U46, u60, u50, The power monitor –16 – Altera Arria V SoC User Manual

Page 36: U46, u60, u50 –16

5–16

Chapter 5: Board Test System

The Power Monitor

Arria V SoC Development Kit

June 2014

Altera Corporation

User Guide

The Power Monitor

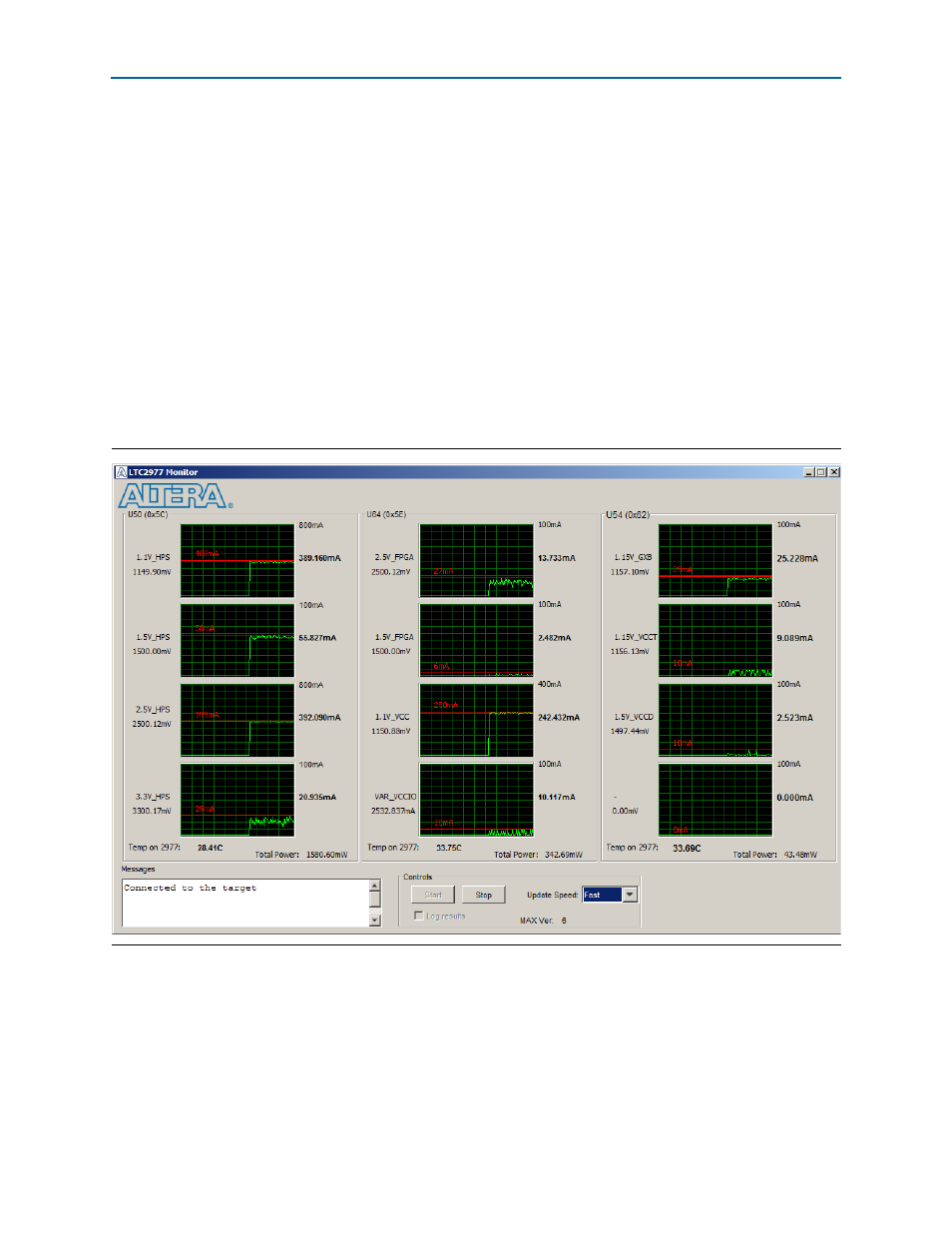

The Power Monitor measures and reports current power

information. To start the

application, click Power Monitor in the Board Test System application.

1

You can also run the Power Monitor as a stand-alone application. PowerMonitor.exe

resides in the

In Windows, click Start > All Programs > Altera > Arria V SoC Development Kit

<version> > Power Monitor to start the application.

The Power Monitor communicates with the MAX V device on the board through the

JTAG bus. A power monitor circuit attached to the MAX V device allows you to

measure the power that the Arria V FPGA is consuming.

shows the Power

Monitor.

The following sections describe the Power Monitor controls.

U46, U60, U50

The three groups show the power rail graphs from the three LTC2977 power monitors

on the board:

U46—

HPS Power Monitor

Figure 5–9. The Power Monitor