Restoring the max v cpld to the factory settings – Altera Arria V SoC User Manual

Page 16

3–6

Chapter 3: Board Setup and Defaults

Restoring the MAX V CPLD to the Factory Settings

Arria V SoC Development Kit

June 2014

Altera Corporation

User Guide

For more information about the FPGA board settings, refer to the

.

Restoring the MAX V CPLD to the Factory Settings

This section describes how to restore the original factory contents to the MAX V

CPLD on the development board. Make sure you have the Nios II EDS installed, and

then perform these steps:

1. Set the board switches to the factory default settings described in

Switch and Jumper Settings” on page 3–1

.

1

DIP switch SW4.4 includes the MAX V device in the JTAG chain.

2. Launch the Quartus II Programmer.

3. Click Auto Detect.

4. Click Add File and select

dir>\kits\arriaVST_5astfd5kf40es_soc\factory_recovery\max

5. Turn on the Program/Configure option for the added file.

6. Click Start to download the selected configuration file to the MAX V CPLD.

Configuration is complete when the progress bar reaches 100%.

f

To ensure that you have the most up-to-date factory restore files and product

information, refer to the

page of the Altera website.

Restoring the CFI Flash Device to the Factory Defaults

To program the factory image to the flash device in the Quartus II Programmer, do the

following steps:

1. On the Tools menu in the Quartus II software, click Programmer.

2. In the Programmer window, click Auto-Detect.

1

If you do not see USB Blaster or the board's embedded USB Blaster II listed

next to Hardware Setup, refer to the

“Installing the USB-Blaster II Driver”

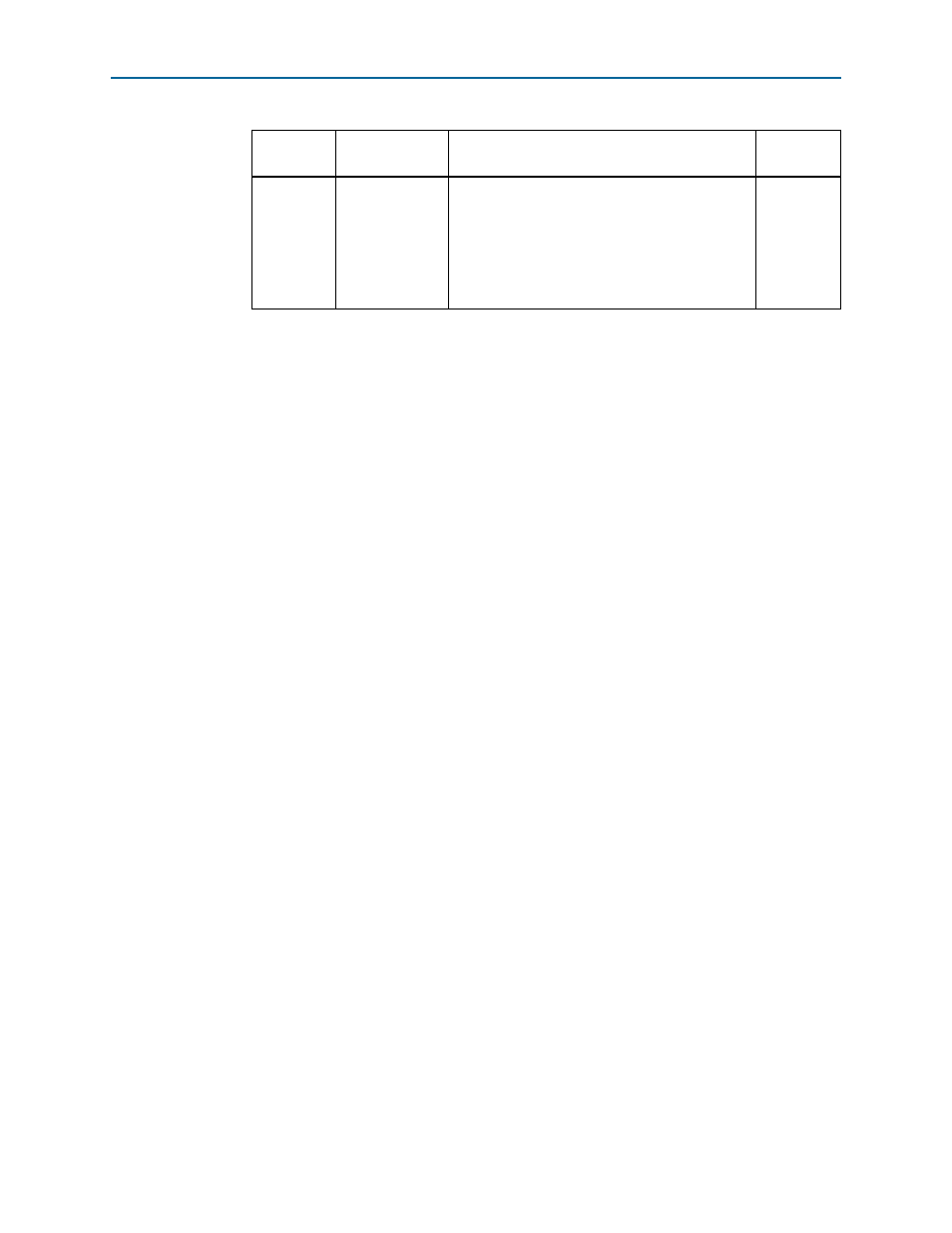

J45, J46

OSC2_CLK_SEL

■

00 (SHORT, SHORT): Selects the on-board

25MHz clock

■

01 (SHORT, OPEN): Selects SMA

■

10 (OPEN, SHORT): Selects the on-board

33MHz clock

■

11 (OPEN, OPEN): none

SHORT,

SHORT

Note to

:

(1) For more information, refer to the

Table 3–4. Default Jumper Settings (Continued)

Board

Reference

Board Label

Description

Default

Position