Altera Nios II C2H Compiler User Manual

Page 88

3–48

9.1

Altera Corporation

Nios II C2H Compiler User Guide

November 2009

Scheduling

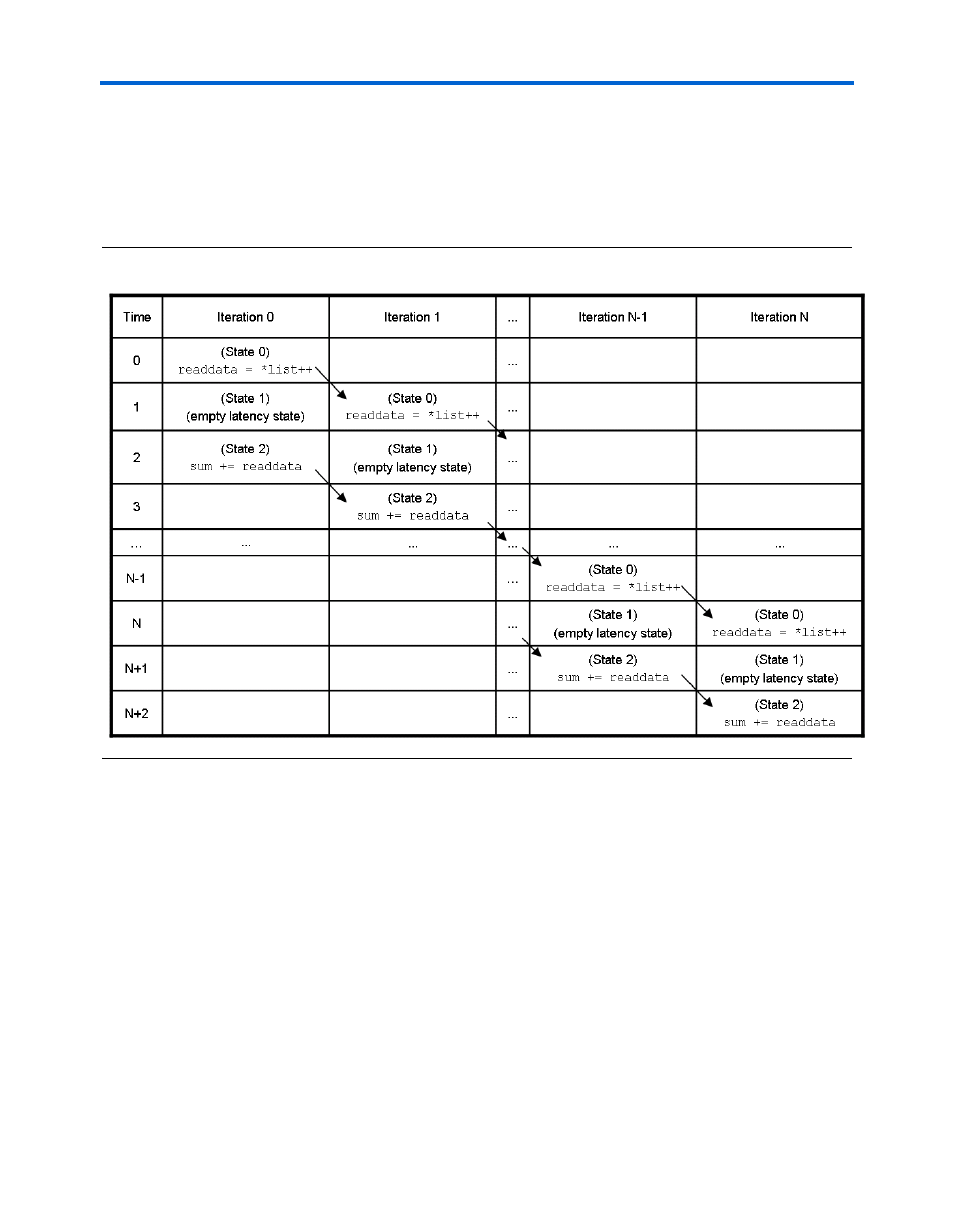

State 1 in

remains empty because

list

has two cycles of read

latency. The loop-carried dependencies on variables

sum

and

list

are

ideal cases, which do not impose restrictions on the pipeline scheduling.

illustrates how the C2H Compiler schedules successive

iterations of the loop.

Figure 3–25. Pipelined Loop Iterations Reading Memory with Latency

, the C2H Compiler is able to start a new iteration

of the loop immediately after the prior iteration completes State 0. At

Time 1, Iteration 1 starts a new read access from

list

, even though data

from

list

hasn't returned for Iteration 0. Due to the two cycles of read

latency, at any given time, there can be a maximum of two pending read

operations.

Over successive iterations of a loop, the C2H Compiler hides the memory

latency by pipelining the read transfers. Although multiple cycles of

latency are required to fill the pipeline, successive iterations can complete

at a rate of one per clock cycle, assuming no stalling occurs (see section

).