Master-slave connections – Altera Nios II C2H Compiler User Manual

Page 63

Altera Corporation

9.1

3–23

November 2009

Nios II C2H Compiler User Guide

C-to-Hardware Mapping Reference

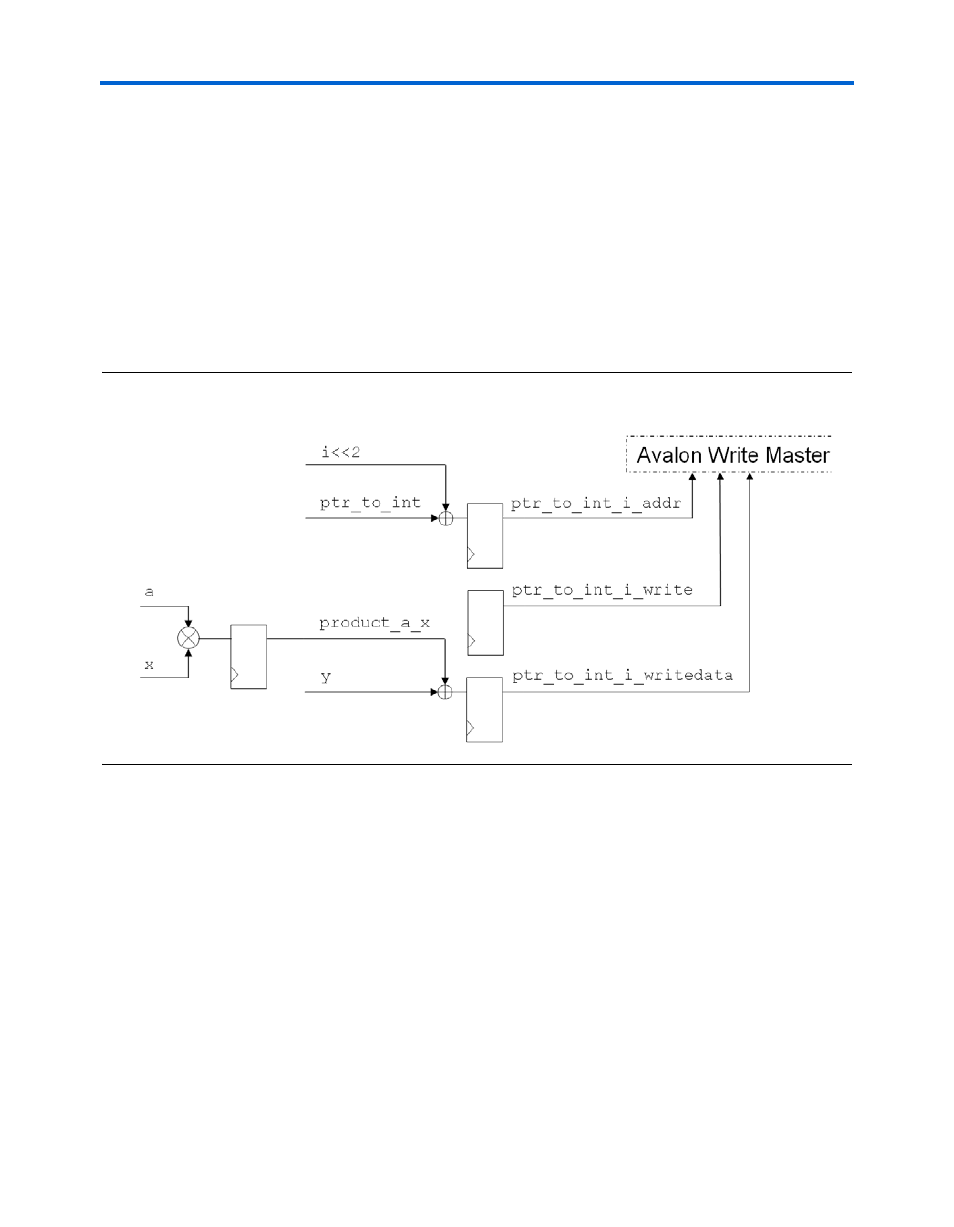

The write-data signal for the Avalon-MM master port is computed and

registered in parallel with the address assignment. As soon as

ptr_to_int_i_addr

and

ptr_to_int_i_writedata

are valid,

write-enable control logic asserts the signal

ptr_to_int_i_write

,

which initiates a transfer on the master port.

shows the logic created for the following write operation to a

dereferenced pointer. Translation of the data-computation logic follows

the rules described in section

*(ptr_to_int + i) = a*x + y;

Figure 3–11. Complex Write Operation

Master-Slave Connections

The C2H Compiler uses pragmas that allow user control of master-slave

connections and arbitration shares. This section describes the pragmas to

control master-slave connections.

The C language specification dictates that when a compiler

implementation encounters a

pragma

directive it does not recognize, the

compiler ignores the pragma. By using pragmas, you can write directives

to optimize the C2H Compiler results, without making the C code

incompatible with other compilers.