Altera Nios II C2H Compiler User Manual

Page 86

3–46

9.1

Altera Corporation

Nios II C2H Compiler User Guide

November 2009

Scheduling

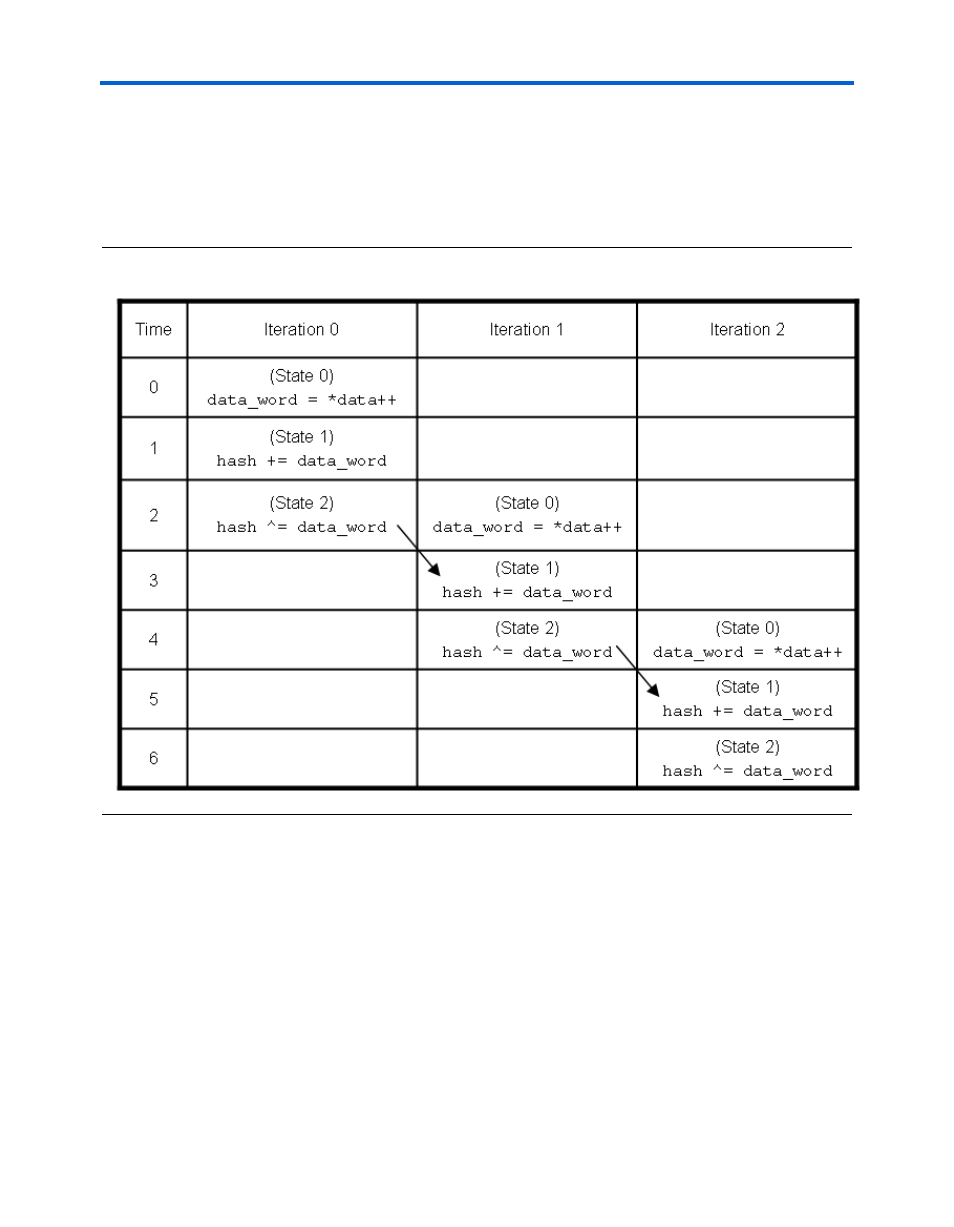

illustrates how the C2H Compiler schedules successive

iterations of the loop shown in

, based on the restrictions

imposed by

hash

. State 1 cannot execute until the previous iteration has

completed State 2. The C2H Compiler schedules the states as shown in

to satisfy the loop-carried dependency.

Figure 3–23. Pipelined Loop Iterations with a Loop-Carried Dependency

In

, the cyclic arrow for

hash

in

translates to

straight arrows between iterations.

Pipelining Avalon-MM Read Transfers from Multiple Iterations

As discussed in section

“Read Operations with Latency” on page 3–37

,

the C2H Compiler is aware of read latency in slave memories. Master

ports on C2H accelerators can use Avalon-MM pipelined read transfers,

which allow multiple read transfers to be pending at a given time. As a

result, for a loop that reads from memory with latency, the next iteration

of the loop can begin fetching data before data from the previous iteration

has returned. For such a loop, the C2H Compiler creates a master port