Altera Nios II C2H Compiler User Manual

Page 52

3–12

9.1

Altera Corporation

Nios II C2H Compiler User Guide

November 2009

One-to-One C-to-Hardware Mapping

shows an example of a subfunction called by two different

functions. In this case, functions

foo()

and

bar()

both call a

subfunction

foobar_sub()

.

shows the hardware structure of the accelerators resulting

from the code in

. Logic for the function

foobar_sub()

exists

within both accelerators.

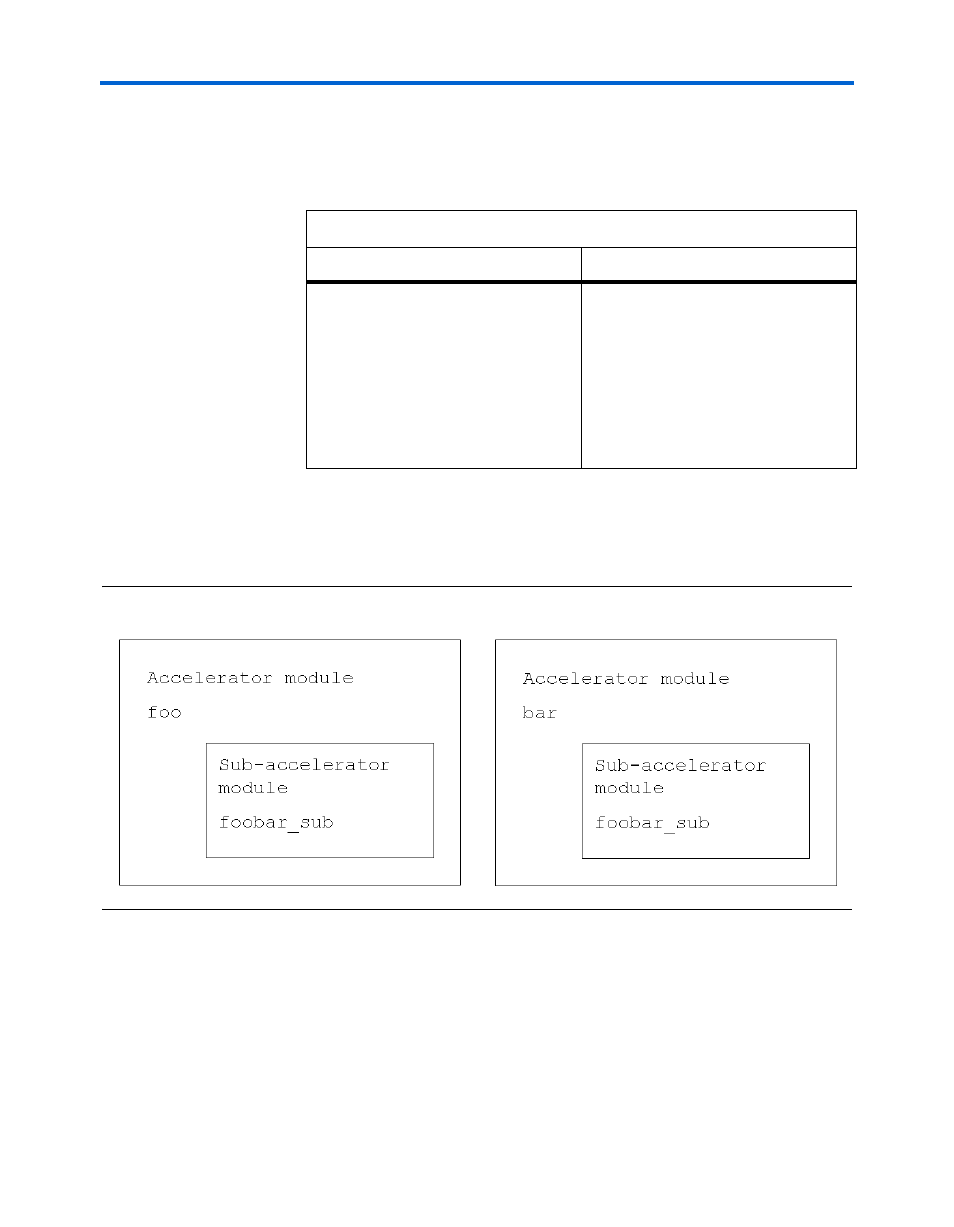

Figure 3–8. Shared Subfunction Logic

The C2H Compiler does not support external subfunctions. You must

locate the subfunction in the same source file as the accelerated function.

This is because, unlike the

#include

construct, a C external function

reference requires the presence of a linker. The C2H Compiler has no

linker.

Table 3–5. Shared Subfunction foobar_sub()

Top-Level Accelerated Function: foo() Top-Level Accelerated Function: bar()

void foo(int *data_in,

int *data_out)

{

...

foobar_sub();

...

}

void bar(int *data_in,

int *data_out)

{

...

foobar_sub();

...

foobar_sub();

...

}

- MAX 10 JTAG (15 pages)

- MAX 10 Power (21 pages)

- Unique Chip ID (12 pages)

- Remote Update IP Core (43 pages)

- Device-Specific Power Delivery Network (28 pages)

- Device-Specific Power Delivery Network (32 pages)

- Hybrid Memory Cube Controller (69 pages)

- ALTDQ_DQS IP (117 pages)

- MAX 10 Embedded Memory (71 pages)

- MAX 10 Embedded Multipliers (37 pages)

- MAX 10 Clocking and PLL (86 pages)

- MAX 10 FPGA (26 pages)

- MAX 10 FPGA (56 pages)

- USB-Blaster II (22 pages)

- GPIO (22 pages)

- LVDS SERDES (27 pages)

- User Flash Memory (33 pages)

- ALTDQ_DQS2 (100 pages)

- Avalon Tri-State Conduit Components (18 pages)

- Cyclone V Avalon-MM (166 pages)

- Cyclone III FPGA Starter Kit (36 pages)

- Cyclone V Avalon-ST (248 pages)

- Stratix V Avalon-ST (286 pages)

- Stratix V Avalon-ST (293 pages)

- DDR3 SDRAM High-Performance Controller and ALTMEMPHY IP (10 pages)

- Arria 10 Avalon-ST (275 pages)

- Avalon Verification IP Suite (224 pages)

- Avalon Verification IP Suite (178 pages)

- FFT MegaCore Function (50 pages)

- DDR2 SDRAM High-Performance Controllers and ALTMEMPHY IP (140 pages)

- Floating-Point (157 pages)

- Integer Arithmetic IP (157 pages)

- Embedded Peripherals IP (336 pages)

- JESD204B IP (158 pages)

- Low Latency Ethernet 10G MAC (109 pages)

- LVDS SERDES Transmitter / Receiver (72 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (3 pages)

- Nios II Embedded Evaluation Kit Cyclone III Edition (80 pages)

- IP Compiler for PCI Express (372 pages)

- Parallel Flash Loader IP (57 pages)

- RAM-Based Shift Register (26 pages)

- RAM Initializer (36 pages)

- Phase-Locked Loop Reconfiguration IP Core (51 pages)

- DCFIFO (28 pages)