Technical details, 8technical details, 1 technical details – Pilz PSSu E S INC User Manual

Page 45

Pilz GmbH & Co. KG, Felix-Wankel-Straße 2, 73760 Ostfildern, Germany

Telephone: +49 711 3409-0, Telefax: +49 711 3409-133, E-Mail: [email protected]

8-1

8.1

Technical details

8

Technical details

8

8000

Technical details

Technical details

8-

8.1

Technical details

8100

Technical details

8-

][Technische Daten PSSu ST-Zähler

Technical details

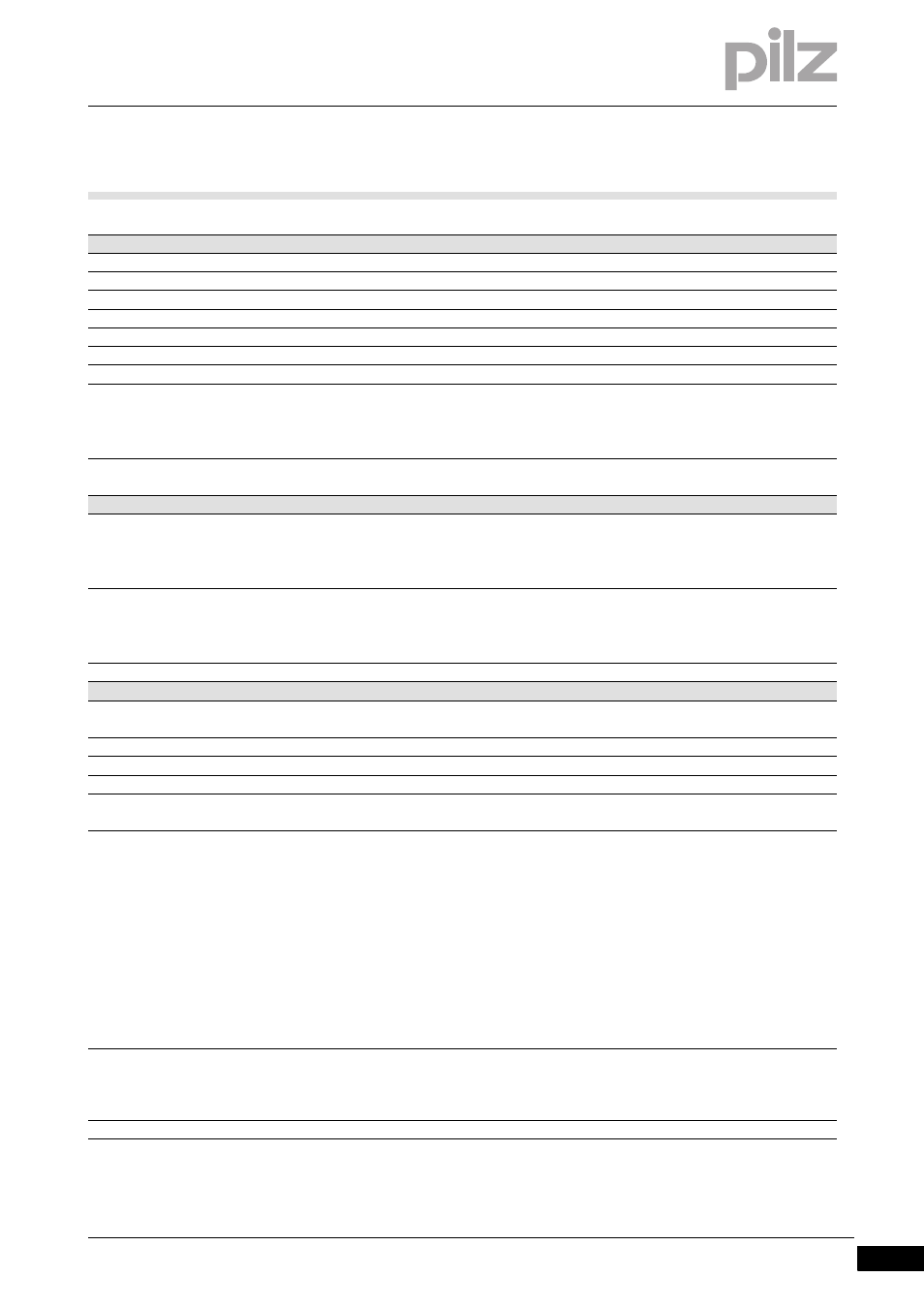

Application range

Standard

Module's device code

0321h

Number of ST input bits

64

Number of ST output bits

32

Number of ST status bits

8

Number of ST control bits

8

Support in system environment A

from ST firmware version for other head modules

11

from ST firmware version PSSu H S PN

2

from ST firmware version PSSu WR S IDN

4

Support in system environment B

from head module ST firmware version

1.0.0

Electrical data

Internal supply voltage (module supply)

Supply voltage range of module supply

4.8 - 5.4 V

Module's current consumption

157 mA

Module's power consumption

0.79 W

Periphery's supply voltage (periphery supply)

Voltage range

16.8 - 30.0 V

Module's current consumption with no load

15 mA

Module's power consumption with no load

0.37 W

Max. power dissipation of the module

1.20 W

Counter interface

Number of counter inputs

1

Type of counter inputs

Incremental encoder

Max. number of bits on the counter input

32 Bit

Evaluation of counter pulses

1x, 2x, 4x

Maximum threshold frequency

5.0 MHz

Phase offset between differential signals A and B

90 deg

Phase offset tolerance

30 deg

Signal at counter inputs A and B and/or C

Differential signal (RS 422)

Time constant of input filter on LATCH signal

50 µs

Time constant of input filter on GATE signal

50 µs

Time constant of input filter on STATUS signal

50 µs

Permitted low signal range on LATCH/GATE/STATUS sig-

nals

-3 - 5 V

Permitted high signal range on LATCH/GATE/STATUS sig-

nals

11 - 30 V

Typ. input current of the LATCH and/or GATE and/or STA-

TUS signals at low level

0 mA

Typ. input current of the LATCH and/or GATE and/or STA-

TUS signals at high level

4.0 mA

Potential isolation between input/output and periphery

supply

yes

Potential isolation between input/output and voltage for

the internal module bus

yes

Typ. processing time

0.1 ms