Digilent 410-178P-KIT User Manual

Page 8

Atlys Reference Manual

www.digilentinc.com

page 8 of 22

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

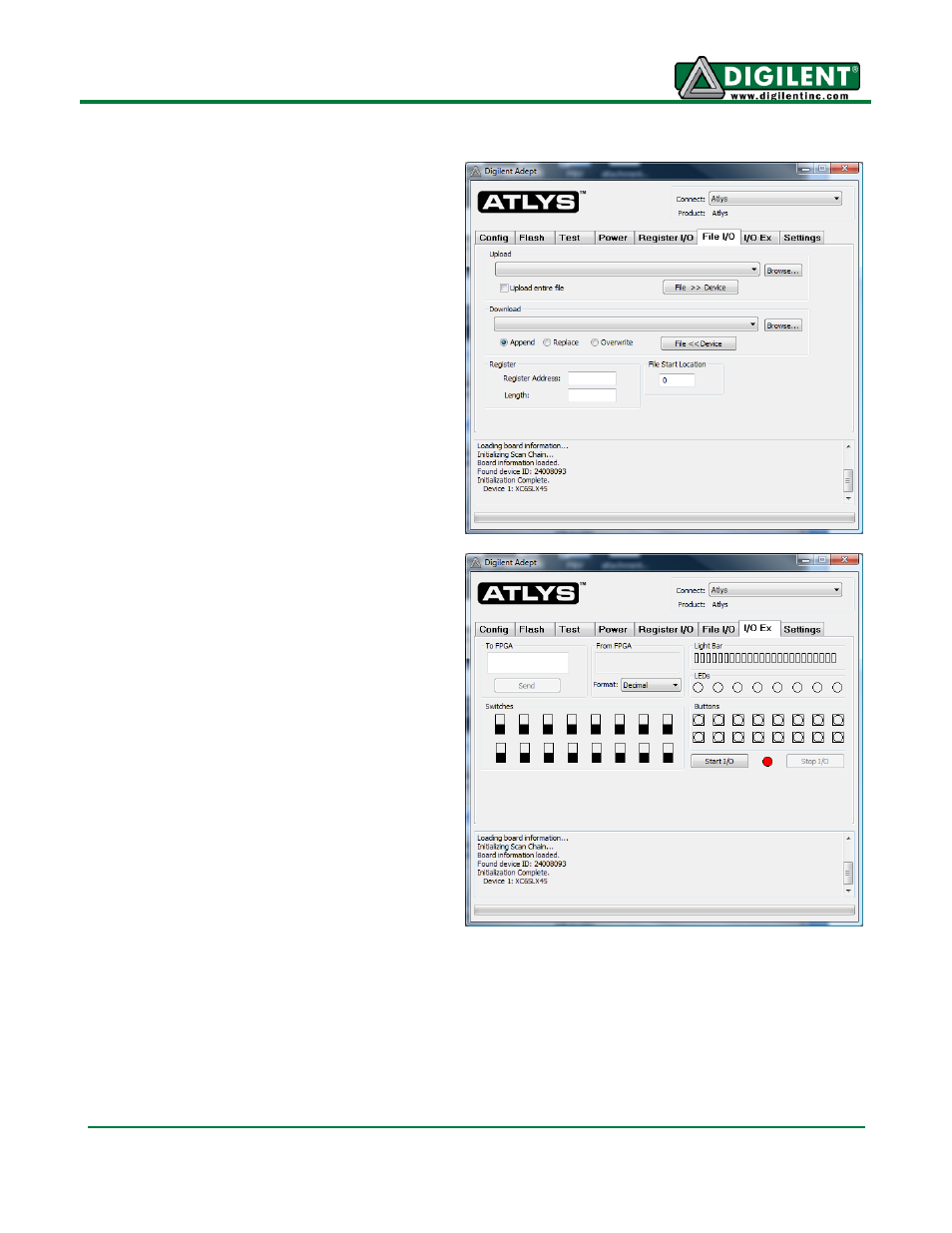

File I/O

The File I/O tab can transfer files between the

PC and the Atlys FPGA. A number of bytes

(specified by the Length value) can be

streamed into a specified register address from

a file or out of a specified register address into

a file. During upload and download, the file

start location can be specified in terms of

bytes.

As with the Register I/O tab, File I/O also

requires specific IP to be available in the

FPGA. This IP can include a memory

controller for writing files into the on-board

DDR2 and Flash memories.

I/O Expand

The I/O Expand tab works with an IP block in

the FPGA to provide additional simple I/O

beyond the physical devices found on the Atlys

board. Virtual I/O devices include a 24-LED

light bar, 16 slide switches, 16 push buttons, 8

discrete LEDs, a 32-bit register that can be

sent to the FPGA, and a 32-bit register that can

be read from the FPGA. The IP block, available

in the Adept I/O Expansion reference design

(AdeptIOExpansion.zip) on the Adept page of

the Digilent website, provides a simple

interface with well-defined signals. This IP

block can easily be included in, and accessed

from, user-defined circuits.

For more information, see the Adept

documentation available at the Digilent

website.