Features, Configuration, Spartan-6 – Digilent 410-178P-KIT User Manual

Page 2

Atlys Reference Manual

www.digilentinc.com

page 2 of 22

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

Features

Xilinx Spartan-6 LX45 FPGA, 324-pin BGA package

128Mbyte DDR2 with 16-bit wide data

10/100/1000 Ethernet PHY

on-board USB2 ports for programming and data transfer

USB-UART and USB-HID port (for mouse/keyboard)

two HDMI video input ports and two HDMI output ports

AC-97 Codec with line-in, line-out, mic, and headphone

real-time power monitors on all power rails

16Mbyte x4 SPI Flash for configuration and data storage

100MHz CMOS oscillator

48 I/O’s routed to expansion connectors

GPIO includes eight LEDs, six buttons, and eight slide switches

ships with a 20W power supply and USB cable

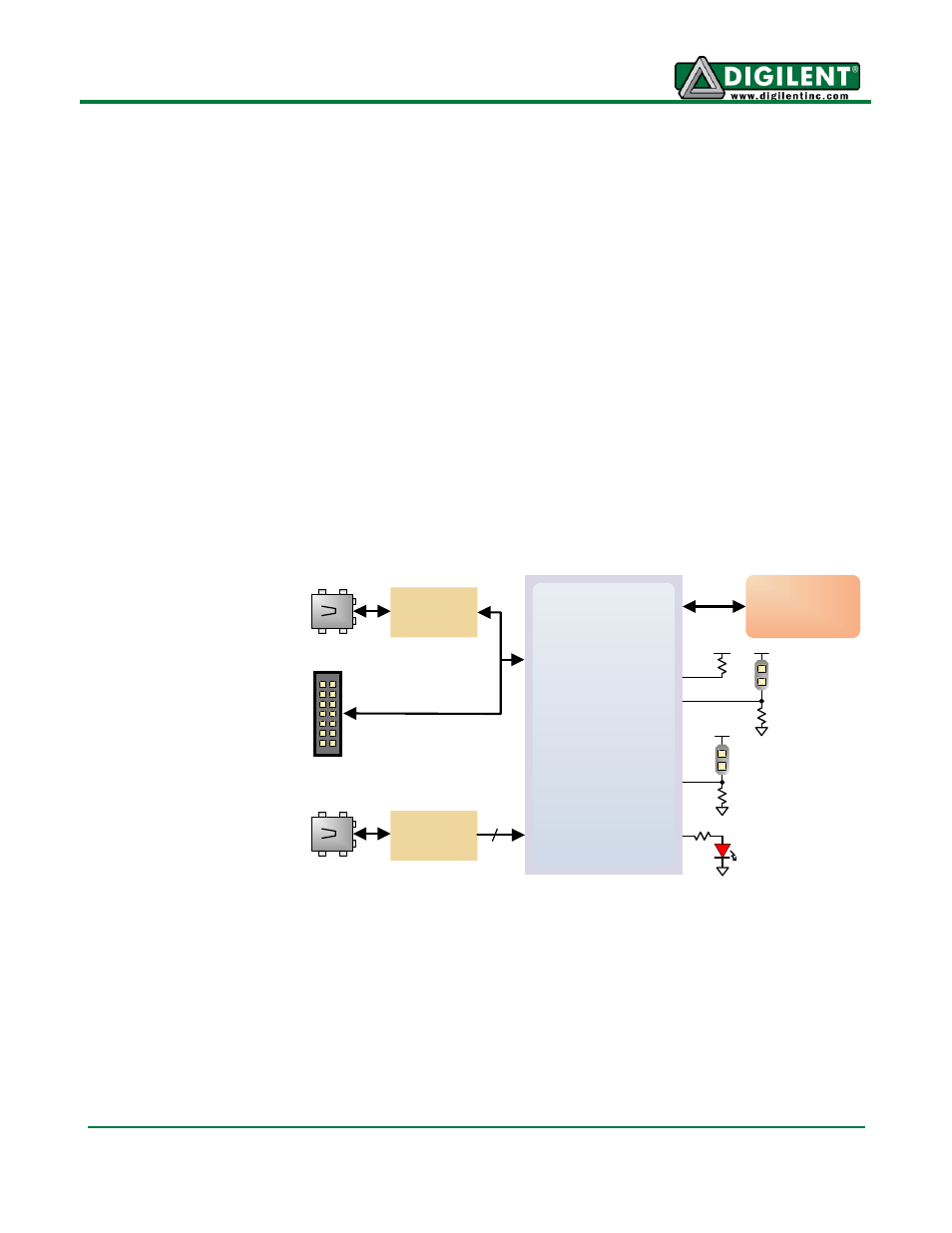

Configuration

After power-on, the

FPGA on the Atlys

board must be

configured (or

programmed) before it

can perform any

functions. The FPGA

can be configured in

three ways: a USB-

connected PC can

configure the board

using the JTAG port any

time power is on, a

configuration file stored

in the SPI Flash ROM

can be automatically

transferred to the FPGA

at power-on, or a

programming file can be transferred from a USB memory stick attached to the USB HID port.

An on-board mode jumper (JP11) selects between JTAG/USB and ROM programming modes. If JP11

is not loaded, the FPGA will automatically configure itself from the ROM. If JP11 is loaded, the FPGA

will remain idle after power-on until configured from the JTAG or Serial programming port.

Always keep JP12 loaded (either on 3.3V or 2.5V). If JP12 is not loaded, bank 2 of the FPGA is not

supplied, and neither are the pull-ups for CCLK, DONE, PROGRAM_B and INIT_B. The FPGA is

held in the Reset state, so it is not seen in the JTAG chain, neither can be programmed from the serial

FLASH.

M0

M1

HSWEN

JTAG

Port

USB

Controller

Numonyx SPI

Flash (x4)

16Mbytes

2x7 2mm

Prog. Header

SPI

Port

J17

Adept USB Port

Spartan-6

JP11

JP10

Done

J10

Load to disable

boot from ROM

Load to disable I/O

pull-ups during config

PIC24

J13

Host Port

Serial

Port

2