Rockwell Automation 57C421B Pulsetach Input Module/DCS 5000/AutoMax User Manual

Page 30

4Ć8

multiplied by four. If the bit is set to zero, the incoming pulses are

multiplied by two.

If a singleĆchannel pulsetach is connected to the module, this bit

should be set to zero. Incoming pulses from a singleĆchannel

pulsetach are not multiplied.

Bit: 13

Description: Timer/Counter Select

When this bit is set to one, the module functions as a timer using its

internal 200 kHz clock (no external cabling from the pulsetach is

required). If the bit is set to zero, the module functions as counter

based on pulsetach inputs.

Bit: 14

Description: Counter Clear Inhibit

When this bit is set to one, the counter will not be cleared after an

interrupt while the module is operating in speed detection mode.

Note that bits 3 and 4 of this register must both be set to zero to

activate this feature. When this bit is set to zero, the module will

operate in speed detection mode as described in section 4.1.2; i.e.,

the counter will be cleared after each interrupt.

Bit: 15

Description: System use only.

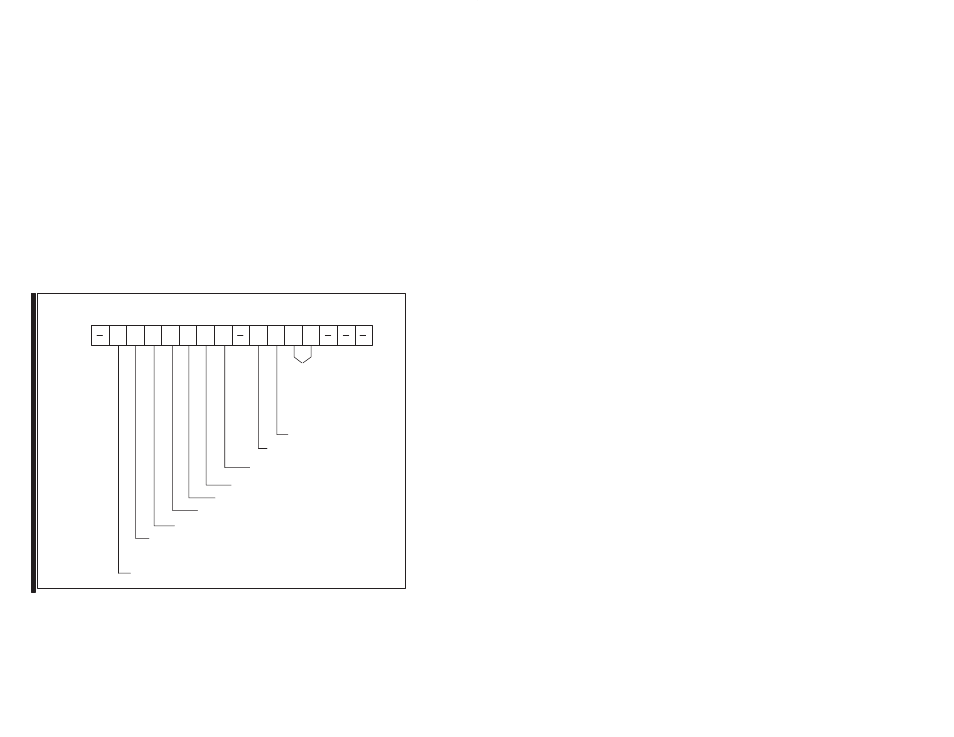

0

1

2

3

4

5

6

7

9

8

10

11

12

13

14

15

Register 5

Bits

rw rw rw rw rw rw rw

rw rw rw rw

Counter clear control

00: Never clear the

counter

01: External latch

10: Comparator equal

11: After counter read

Timer interrupt enable

Generate CCLK

External latch interrupt enable

External count stop interrupt enable

Z pulse and origin interrupt enable

Comparator equal interrupt enable

Pulse multiplier

Timer/counter select

0: Counter

1: Timer

Counter clear inhibit

Figure 4.9 Ć Interrupt Status Control Register (Register 5)