Pin descriptions, 1 analog pins, 1 voltage1 & voltage2 inputs – Cirrus Logic CS5467 User Manual

Page 18: 2 current1 & current2 inputs, 3 power fail monitor input, 4 voltage reference input, 5 voltage reference output, 6 crystal oscillator, 2 digital pins, 1 reset input

CS5467

18

DS714F3

5. PIN DESCRIPTIONS

5.1 Analog Pins

The CS5467 has four differential inputs: VIN1

VIN2

IIN1

, and IIN2 are the voltage1, voltage2, current1,

and current2 inputs, respectively. A single-ended power

fail monitor input, voltage reference input, and voltage

reference output are also available.

5.1.1 Voltage1 & Voltage2 Inputs

The output of the line voltage resistive divider or trans-

former is connected to the VIN1+ (VIN2+) and VIN1-

(VIN2-) input pins of the CS5467. The voltage channel

is equipped with a 10x, fixed-gain amplifier. The

full-scale signal level that can be applied to the voltage

channel is ±250 mV. If the input signal is a sine wave,

the maximum RMS voltage is

250 mVp /

2

176.78 mVRMS which is approximate-

ly 70.7% of maximum peak voltage.

5.1.2 Current1 & Current2 Inputs

The output of the current-sensing resistor or transform-

er is connected to the IIN1+ (IIN2+) and IIN1- (IIN2-) in-

put pins of the CS5467. To accommodate different

current-sensing elements, the current channel incorpo-

rates a programmable gain amplifier (PGA) with two se-

lectable input gains. The full-scale signal level for the

current channels is ±50 mV or ±250 mV. If the input sig-

nal is a sine wave, the maximum RMS voltage is

35.35 mVRMS or 176.78 mVRMS which is approxi-

mately 70.7% of maximum peak voltage.

5.1.3 Power Fail Monitor Input

An analog input (PFMON) is provided to determine

when a power loss is imminent. By connecting a resis-

tive divider from the unregulated meter power supply to

the PFMON input, an interrupt can be generated, or the

Low Supply Detected (LSD) Status register bit can be

monitored to indicate low-supply conditions. The PF-

MON input has a comparator that trips around the level

of the voltage reference input (VREFIN).

5.1.4 Voltage Reference Input

The CS5467 requires a stable voltage reference of

2.5 V applied to the VREFIN pin. This reference can be

supplied from an external voltage reference or from the

VREFOUT output. A bypass capacitor of at least 0.1

F

is recommended at the VREFIN pin.

5.1.5 Voltage Reference Output

The CS5467 generates a 2.5 V reference (VREFOUT).

It is suitable for driving the VREFIN pin, but has very lit-

tle fan-out capacity and is not recommended for driving

external circuits.

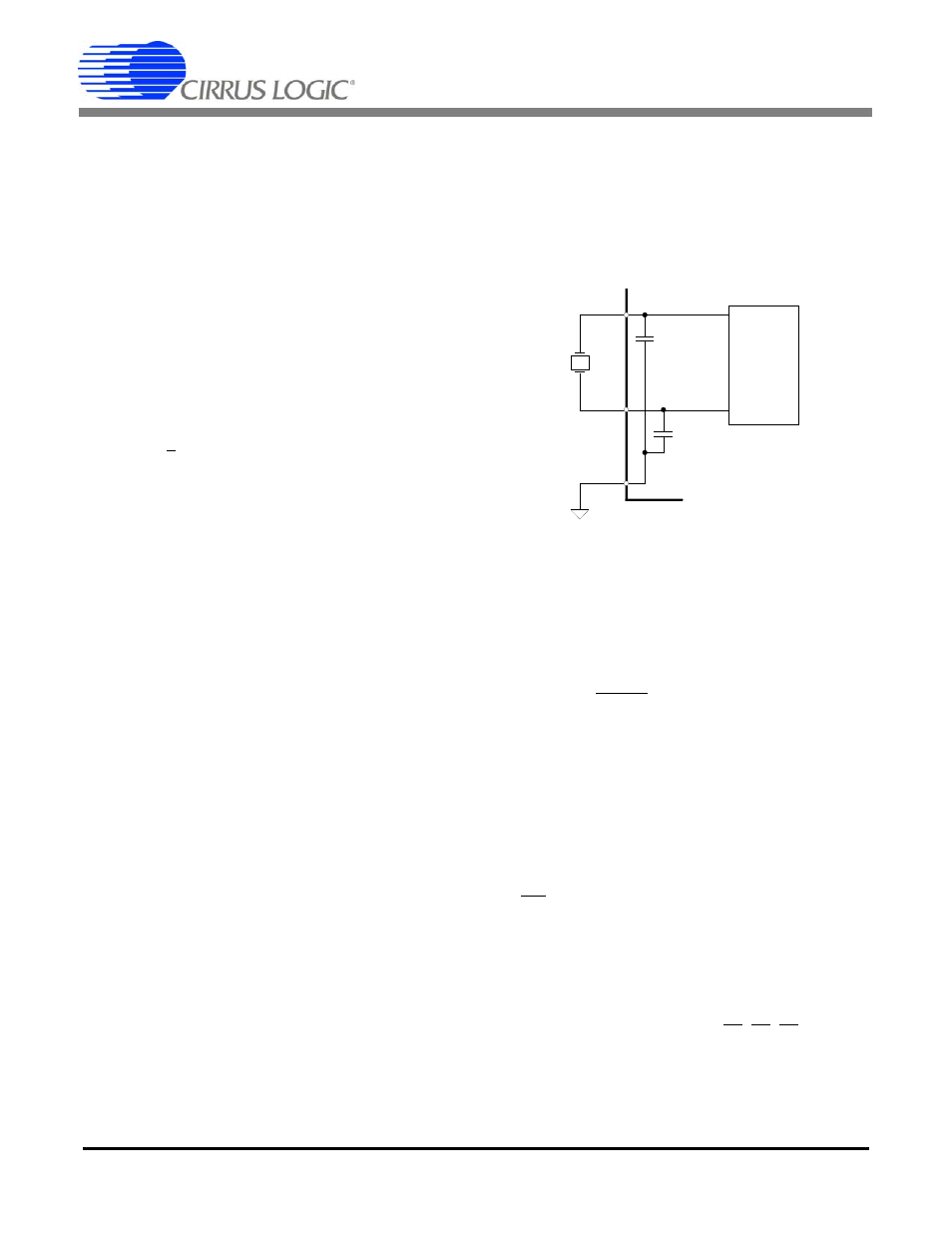

5.1.6 Crystal Oscillator

An external quartz crystal can be connected to the XIN

and XOUT pins as shown in Figure

. To reduce system

cost, each pin is supplied with an on-chip, phase-shift-

ing capacitor to ground.

.

Alternatively, an external clock source can be connect-

ed to the XIN pin.

5.2 Digital Pins

5.2.1 Reset Input

The active-low RESET pin, when asserted, will halt all

CS5467 operations and reset internal hardware regis-

ters and states. When de-asserted, an initialization se-

quence begins, setting default register values.

5.2.2 CPU Clock Output

A logic-level clock output (CPUCLK) is provided at the

crystal frequency to drive an external CPU or microcon-

troller clock. Two phase choices are available.

5.2.3 Interrupt Output

The INT pin indicates an enabled Internal Status regis-

ter (Status) bit is set. Status register bits indicate condi-

tions such as data ready, modulator oscillations, low

supply, voltage sag, current faults, numerical overflows,

and result updates.

5.2.4 Energy Pulse Outputs

The CS5467 provides three pins (E1, E2, E3) for pulse

energy outputs. These pins can also be used to output

other conditions, such as voltage1 sign, power fail mon-

itor, or energy sign.

Figure 7. Oscillator Connections

Oscillator

Circuit

DGND

XIN

XOUT

C1

C1 =

22 pF

C2

C2 =