Power modes, 1 normal operation, 2 power down, mclk enabled – Cirrus Logic CS5374 User Manual

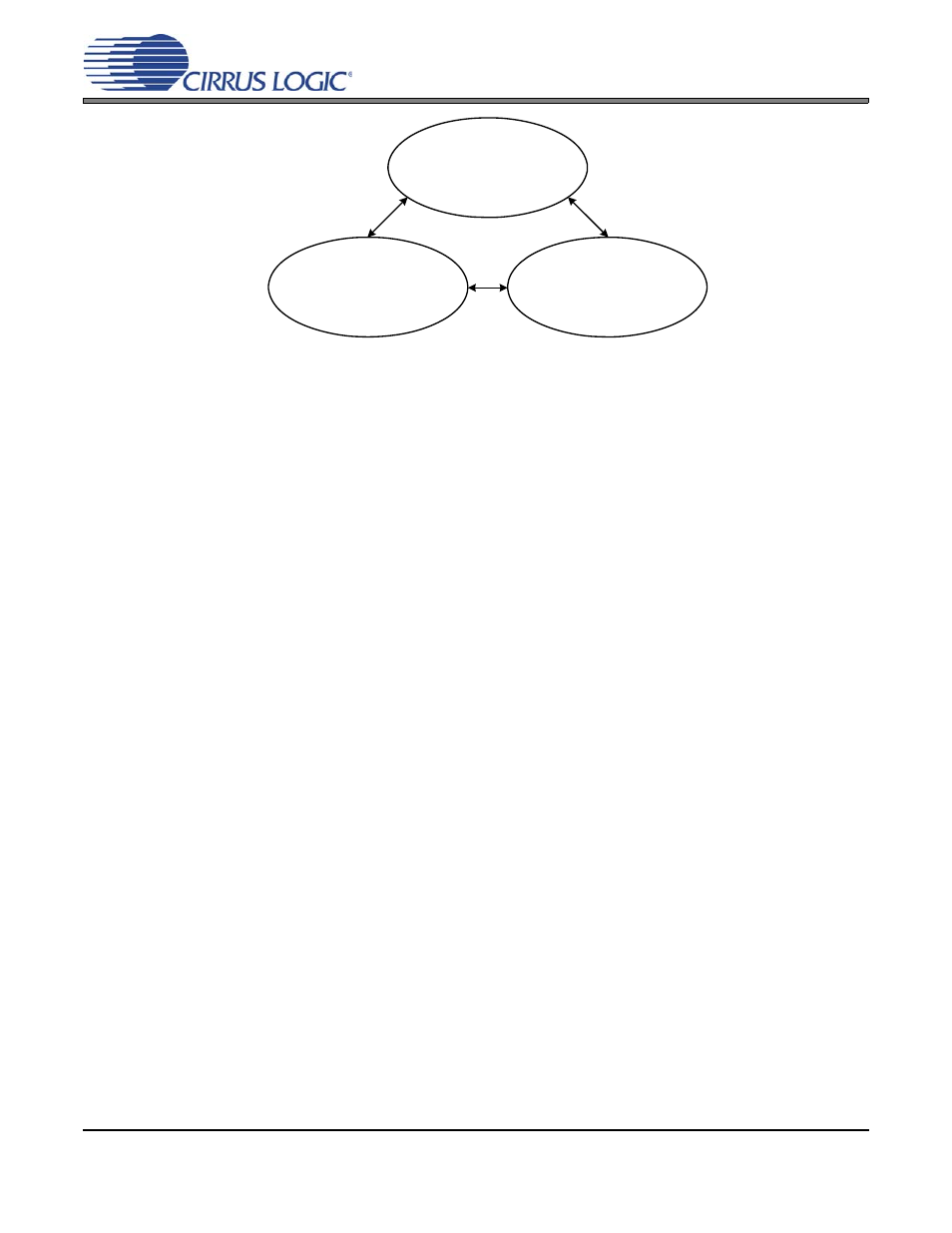

Page 29: 3 power down, mclk disabled, Normal operation, Power down, mclk enabled, Power down, mclk disabled, Figure 17. power mode diagram, Cs5374

CS5374

CS5374

29

6.

POWER MODES

The CS5374 amplifiers and modulators have three

power modes. Normal operation, power down with

MCLK enabled, and power down with MCLK dis-

abled.

Power down mode is controlled by PWDN bits in

the SPI registers, and are active high. When PWDN

is enabled, internal circuitry is disabled, the analog

inputs and outputs go high-impedance, and the de-

vice enters a micro-power state.

6.1 Normal Operation

With MCLK active and the amplifiers and modula-

tors enabled (PWDN = 0) the CS5374 performs

normal data acquisition. A differential analog input

signal is converted to an oversampled 1-bit

ΔΣ bit

stream at 512 kHz. This

ΔΣ bit stream is then digi-

tally filtered and decimated by the CS5376A de-

vice to a high-precision 24-bit output.

6.2 Power Down, MCLK Enabled

With MCLK active and all amplifiers and modula-

tors disabled (PWDN = 1) the CS5374 is placed

into a power-down state. During this power-down

state the amplifiers and modulators are disabled

and all outputs are high impedance. In this mode

power consumption is reduced, but not reduced as

low as with MCLK inactive, as sections of the dig-

ital state machine are kept awake to support SPI

communications. Any unused amplifier/modulator

channels can be turned off individually through the

configuration registers.

6.3 Power Down, MCLK Disabled

If MCLK is stopped, an internal loss-of-clock de-

tection circuit automatically places the CS5374

into a power-down state. This power-down state is

independent of the amplifier and modulator inter-

nal configuration registers, and is automatically in-

voked after approximately 40

μs without receiving

an incoming MCLK edge.

During this power-down state, the amplifiers and

modulators are disabled and all outputs are high

impedance. The entire digital state machine goes

inactive but configuration register values are re-

tained, with a reset required to clear them. When

used with the CS5376A digital filter, the CS5374 is

in this lowest power-down state immediately after

reset since MCLK is disabled by default.

NORMAL OPERATION

MCLK = ON

PWDN registers = disabled

POWER DOWN MODE

MCLK = ON

PWDN registers = enabled

POWER DOWN MODE

MCLK = OFF

PWDN registers = X

Figure 17. Power Mode Diagram