3 spi registers, 1 version — 0x00, 2 amp1cfg — 0x01 – Cirrus Logic CS5374 User Manual

Page 23: 3 amp2cfg — 0x02, Cs5374

CS5374

CS5374

23

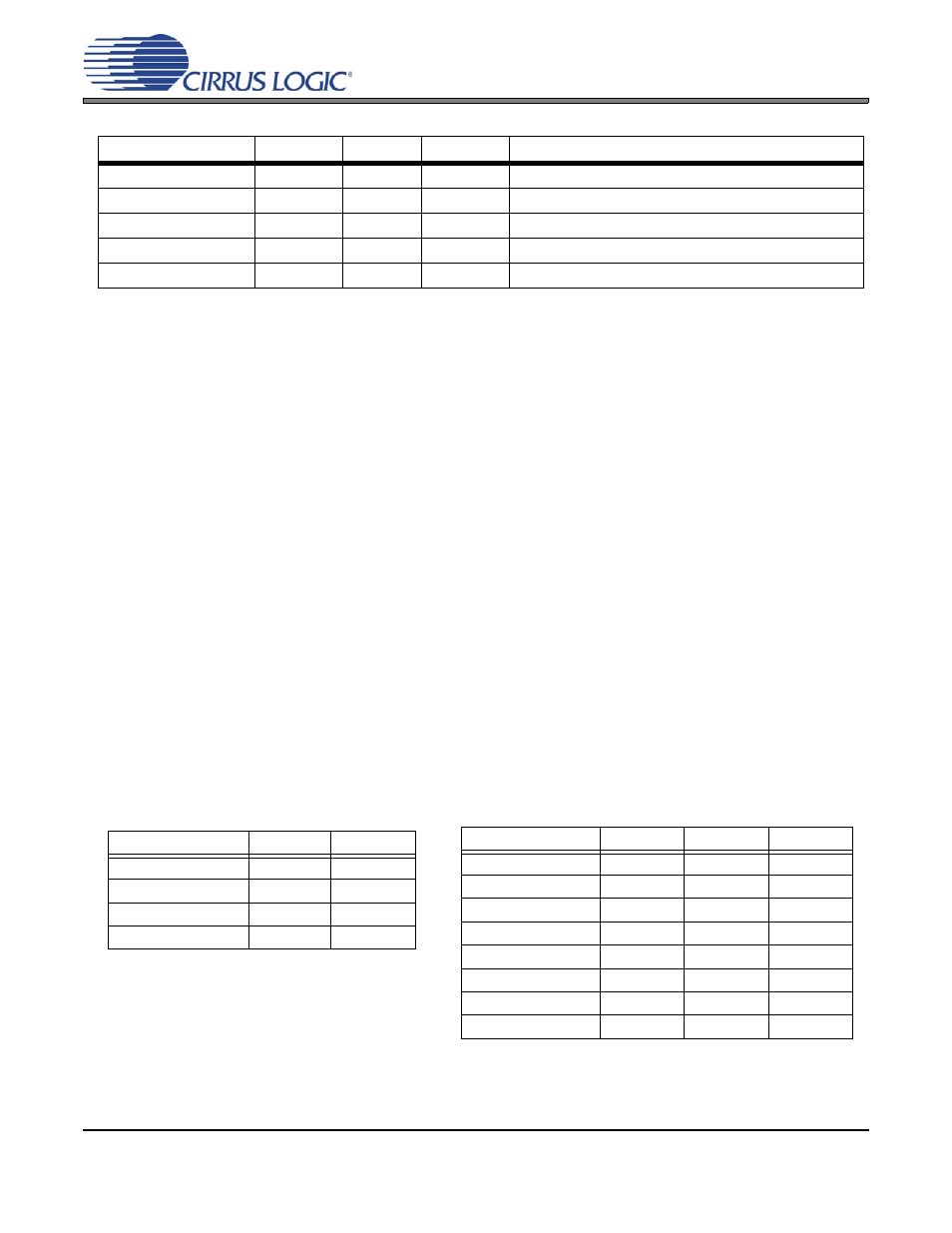

5.3 SPI Registers

The CS5374 SPI registers are 8-bit registers that

control the CS5374 hardware configuration. See

“SPI

Register Summary” on page 34 for de-

tailed bit definitions of the SPI registers listed in

Table 2.

5.3.1 VERSION — 0x00

The VERSION register indicates the hardware re-

vision of the CS5374 device. Read only.

Reset Condition : 0100_0001 (0x41)

Normal Operation : 0100_0001 (0x41)

Power Down Operation : 0100_0001 (0x41)

5.3.2 AMP1CFG — 0x01

The AMP1CFG register controls the amplifier

MUX and GAIN settings for channel 1. It also en-

ables PWDN mode for the channel 1 amplifier plus

enables the GUARD output for channels 1 & 2.

Reset Condition : 0000_0000

Normal Operation : 00MM_0GGG

Power Down Operation : 1000_0000

5.3.3 AMP2CFG — 0x02

The AMP2CFG register controls the amplifier

MUX and GAIN settings for channel 2. It also en-

ables PWDN mode for the channel 2 amplifier.

Reset Condition : 0000_0000

Normal Operation : 00MM_0GGG

Power Down Operation : 1000_0000

Name

Addr.

Type

# Bits

Description

VERSION

0x00

R

8

Device Version ID

AMP1CFG

0x01

R/W

8

Amplifier 1 configuration

AMP2CFG

0x02

R/W

8

Amplifier 2 configuration

ADCCFG

0x03

R/W

8

Modulator 1 & 2 configuration

PWRCFG

0x04

R/W

8

Power configuration

Table 2. SPI Configuration Registers

Gain Selection

GAIN2

GAIN1

GAIN0

1x

0

0

0

2x

0

0

1

4x

0

1

0

8x

0

1

1

16x

1

0

0

32x

1

0

1

64x

1

1

0

reserved

1

1

1

Input Selection

MUX1

MUX0

800

Ω termination

0

0

INA only

1

0

INB only

0

1

INA + INB

1

1

Table 3. Digital Selections for Gain and Input Mux Control