0 hardware – Cirrus Logic CS1810xx User Manual

Page 8

8

©

Copyright 2005 Cirrus Logic, Inc.

DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

Hardware

3.0 Hardware

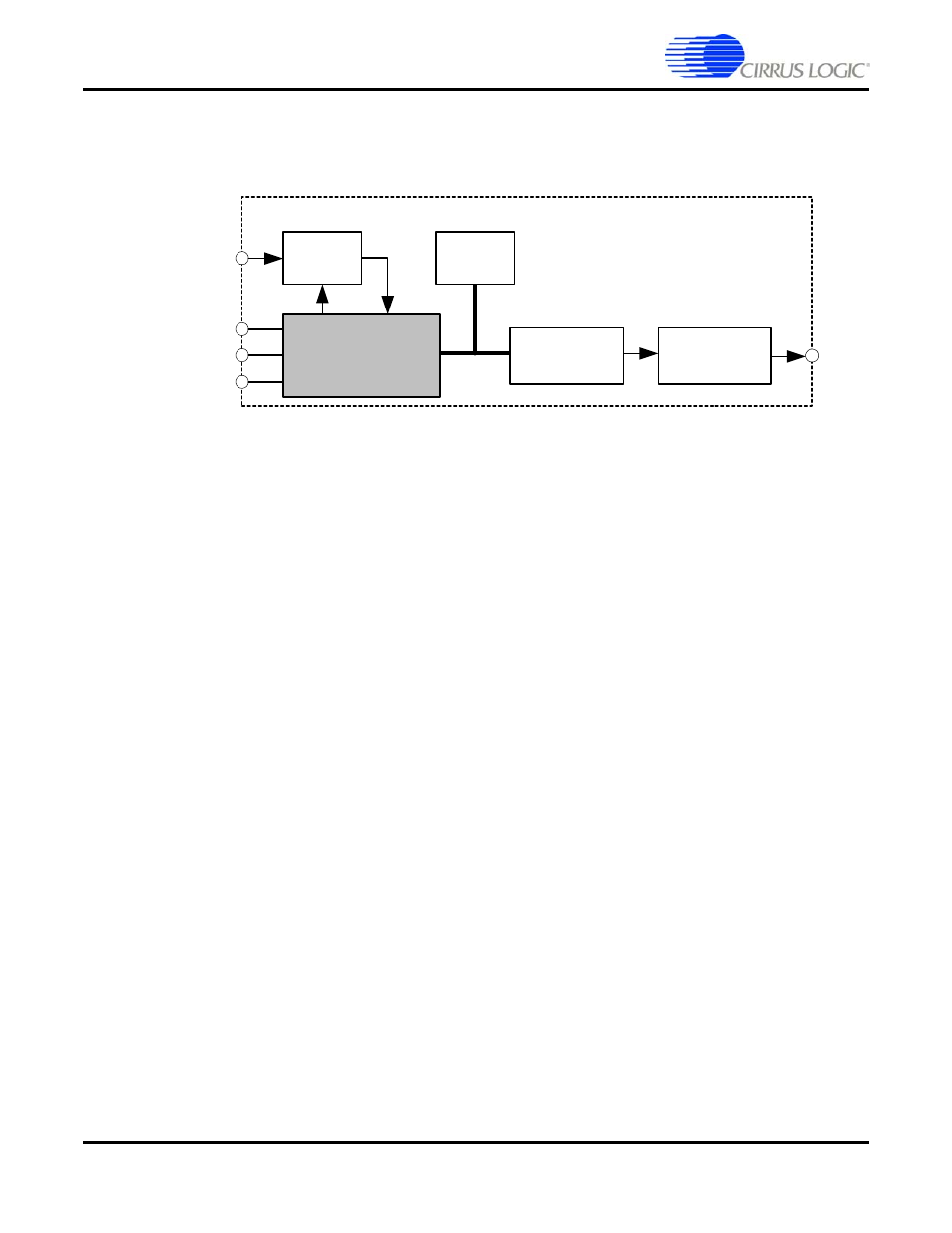

shows a high-level view of the CobraNet CM-2 interface hardware architecture.

Figure 2. CobraNet Interface Hardware Block Diagram

Flash memory holds the CobraNet firmware and management interface variable settings.

The CS1810xx or CS4961xx network processor is the heart of the CobraNet interface. It

implements the network protocol stacks and performs the synchronous-to-isochronous

and isochronous-to-synchronous conversions. The network processor has a role in

sample clock regeneration and performs all interactions with the host system.

The sample clock is generated by a voltage-controlled crystal oscillator (VCXO)

controlled by the network processor. The VCXO frequency is carefully adjusted to achieve

lock with the network clock.

The Ethernet controller is a standard interface chip that implements the 100-Mbit Fast

Ethernet standard. As per Ethernet requirements the interface is transformer isolated.

VCXO

Ethernet

Magnetics

Clock

Audio

Serial

Host

Control

Clock

CobraNet CM-2

Module

Flash

Memory

Ethernet

Controller

CS1810xx/

CS4961xx