Cirrus Logic CS1810xx User Manual

Page 50

50

©

Copyright 2005 Cirrus Logic, Inc.

DS651UM23

Version 2.3

CobraNet Hardware User’s Manual

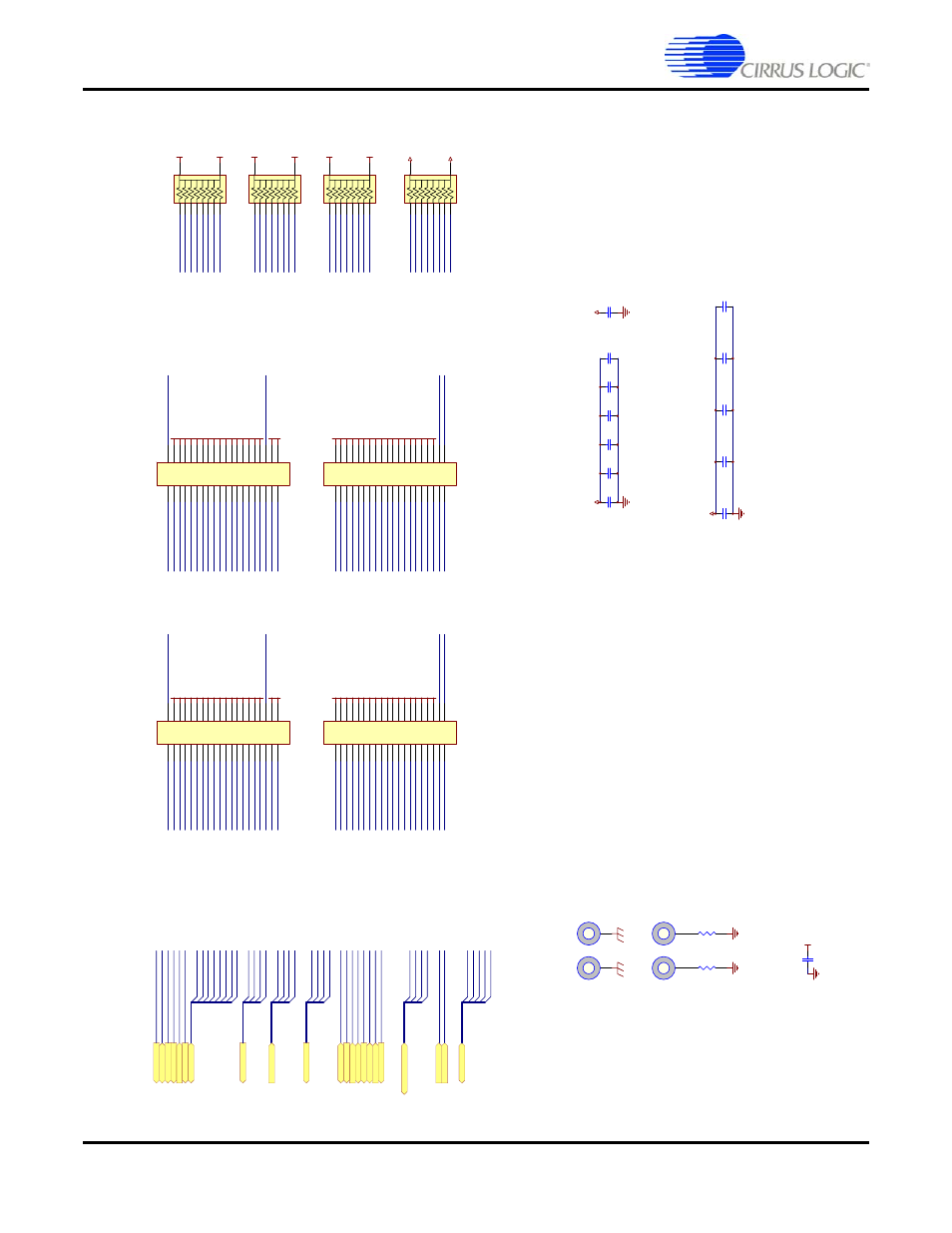

Mechanical Drawings and Schematics

Figure 30. CM-2 RevF Schematic Page 7 of 7

HRESET

#

GN

D

HEN#

GN

D

HRW

GN

D

HREQ#

GN

D

HACK

#

GN

D

HDS#

GN

D

SSI

_CL

K

SSI

_DOUT

0

GN

D

SSI

_DOUT

1

GN

D

SSI

_DOUT

2

GN

D

SSI

_DOUT

3

GN

D

SSI

_DI

N0

GN

D

SSI

_DI

N1

GN

D

SSI

_DI

N2

GN

D

SSI

_DI

N3

GN

D

FS

1

GN

D

M

C

L

K

_OUT

GN

D

MC

LK

_

IN

GN

D

REF

CL

K

_

IN

UART

_RXD

GN

D

U

A

R

T_

TX

D

VCC_+

3.

3

U

A

R

T_

TX

_

O

E

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

HDAT

A0

VCC_+

3.

3

HDAT

A1

VCC_+

3.

3

HDAT

A2

VCC_+

3.

3

HDAT

A3

HDAT

A4

VCC_+

3.

3

HDAT

A5

VCC_+

3.

3

HDAT

A6

VCC_+

3.

3

HDAT

A7

HRESET

#

HADDR0

HEN#

HADDR1

HRW

HADDR2

HREQ#

HRESET

#

HACK

#

HACK

#

HDS#

HDAT

A[

0.

.7

]

SSI

_CL

K

HADDR[

0.

.3

]

SSI

_DOUT

0

SSI

_DOUT

1

SSI

_DOUT

2

SSI

_DOUT

3

SSI

_DI

N0

SSI

_DI

N1

SSI

_DI

N2

SSI

_DI

N3

FS

1

M

C

L

K

_OUT

MC

LK

_

IN

REF

CL

K

_

IN

UART

_RXD

U

A

R

T_

TX

D

U

A

R

T_

TX

_

O

E

HADDR3

MU

TE

#

VCC_+

5

VCC_+

5

HRW

HDS#

HEN#

HREQ#

HDAT

A[

0.

.7

]

HADDR[

0.

.3

]

SSI

_DOUT

[0

..

3

]

S

S

I_

D

IN

[0

..3

]

HDAT

A0

SSI

_DOUT

[0

..

3

]

HDAT

A1

S

S

I_

D

IN

[0

..3

]

HDAT

A2

SSI

_CL

K

HDAT

A3

M

C

L

K

_OUT

HDAT

A4

FS

1

HDAT

A5

U

A

R

T_

TX

D

HDAT

A6

UART

_RXD

HDAT

A7

MC

LK

_

IN

HADDR0

REF

CL

K

_

IN

HADDR1

U

A

R

T_

TX

_

O

E

HADDR2

VCC_+

3.

3

C33

0.

1 uF

C34

0.

1 uF

C35

0.

1 uF

C36

0.

1 uF

C37

0.

1 uF

C38

0.

1 uF

VCC_+

5

C39

0.

1 uF

AC

Sig

nal R

eturn Path C

aps

VCC_+

3.

3

Pow

er

Decoupling

C

aps

AUX_POW

ER0

AUX_POW

ER1

AUX_POW

ER2

AUX_POW

ER3

AUX_POW

ER0

AUX_POW

ER1

AUX_POW

ER2

AUX_POW

ER3

AUX_POW

ER[

0

..

3

]

AUX_POW

ER[

0

..

3

]

W

A

T

C

HDOG

W

A

T

C

HDOG

W

A

T

C

HDOG

MU

TE

#

MU

TE

#

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J3

CNM

_CONN40

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J1

CNM

_CONN40

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J4

CNM

_CONN40

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

B1

B2

B3

B4

B5

B6

B7

B8

B9

B1

0

B1

1

B1

2

B1

3

B1

4

B1

5

B1

6

B1

7

B1

8

B1

9

B2

0

J2

CNM

_CONN40

Note: Sim

ilar

AC

s

ig

n

al r

etur

n path caps

m

u

st

be included on the m

o

ther

boar

d near

the connector

.

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

GN

D

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

VCC_+

3.

3

HRESET

#

HEN#

HRW

HREQ#

HACK

#

HDS#

SSI

_CL

K

SSI

_DOUT

0

SSI

_DOUT

1

SSI

_DOUT

2

SSI

_DOUT

3

SSI

_DI

N0

SSI

_DI

N1

SSI

_DI

N2

SSI

_DI

N3

FS

1

MC

LK

_

O

U

T

MC

LK

_

IN

REF

CL

K

_

IN

UART

_RXD

UART

_T

XD

U

A

R

T_

TX

_

O

E

HADDR3

MU

TE

#

VCC_+

5

VCC_+

5

HDAT

A0

HDAT

A1

HDAT

A2

HDAT

A3

HDAT

A4

HDAT

A5

HDAT

A6

HDAT

A7

HADDR0

HADDR1

HADDR2

AUX_POW

ER0

AUX_POW

ER1

AUX_POW

ER2

AUX_POW

ER3

W

A

T

C

HDOG

1

M3

M

OUNT

IN

G

1

M4

M

OUNT

IN

G

1

M2

M

OUNT

IN

G

1

M1

M

OUNT

IN

G

R40

0 Ohm

R39

0 Ohm

T

h

es

e two

m

o

unting

ho

le

s are

l

o

cate

d at the

"

b

ack"

o

f the

CM

-2,

ne

ar the

m

ain inte

rf

ace

co

nne

cto

rs.

T

h

es

e two

m

o

unting

ho

le

s are

l

o

cate

d ne

ar

the

f

ro

n

t pane

l o

f the

CM

-2.

C10

10 uF

, X5R,

6.

3 Vo

lt

s

C11

10 uF

, X5R,

6.

3 Vo

lt

s

C12

10 uF

, X5R,

6.

3 Vo

lt

s

C13

10 uF

, X5R,

6.

3 Vo

lt

s

C14

10 uF

, X5R,

6.

3 Vo

lt

s

RSVD3

RSVD3

RSVD1

RSVD2

RSVD4

RSVD1

RSVD2

RSVD4

HADDR3

HADDR0

HADDR1

HADDR2

HDAT

A0

HDAT

A1

HDAT

A2

HDAT

A3

HDAT

A4

HDAT

A5

HDAT

A6

HDAT

A7

HEN#

HDS#

HACK

#

HREQ#

U

A

R

T_

TX

_

O

E

U

A

R

T_

TX

D

UART

_RXD

REF

CL

K

_

IN

GN

D

SSI

_DOUT

3

RSVD2

RSVD4

RSVD5

SSI

_DI

N0

SSI

_DI

N1

SSI

_DI

N2

SSI

_DI

N3

RSVD3

FS

1

SSI

_CL

K

N

o

te

: P

u

ll

-u

p

s/

d

o

w

n

s o

n

S

S

I_

D

O

U

T

[0

..4

] a

re

l

o

ca

te

d

o

n

t

h

e D

S

P

s

ch

em

at

ic

p

ag

e.

MC

LK

_

IN

T

h

es

e pul

lups/do

wns are

use

d to

assure

a v

al

id l

o

g

ic l

ev

el

if

a sig

nal

is

tri-state

d o

r no

t co

nne

cte

d.

I

n

so

m

e situatio

ns,

the

se

m

ay

no

t be

re

quire

d.

C50

0.

01 uF

, 2K

V

SHI

EL

D

Place near

the E

ther

net connector

s.

1

2

3

4

5

6

7

8

9

10

RN3

10K

Ohm

, 8x Array

1

2

3

4

5

6

7

8

9

10

RN4

10K

Ohm

, 8x Array

1

2

3

4

5

6

7

8

9

10

RN5

10K

Ohm

, 8x Array

1

2

3

4

5

6

7

8

9

10

RN6

10K

Ohm

, 8x Array

GN

D

GN

D

GN

D

GN

D

GN

D

VCC_+

3.

3

VCC_+

3.

3

HADDR3

RSVD[

1.

.5

]

RSVD[

1.

.5

]

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5